# **NXP Semiconductors**

#### Hardware Design Guidelines for S32K3xx Microcontrollers

Rev. E2 - March. 2025

**AES MCU Applications Engineering**

#### 1 Introduction

The S32K3XX Microcontroller further extends the highly scalable portfolio of Arm® Cortex® MCUs in the automotive industry. It builds on the legacy of the S32K series, while introducing higher memory options alongside a richer peripheral set extending capability into a variety of automotive applications.

With a +2.97V - +5.5V supply and focus on automotive environment robustness, the S32K3 series devices are well suited to a wide range of applications in electrical harsh environments. These devices are optimized for cost-sensitive applications offering low pin-count options.

The purpose of this application note is to describe possible hardware considerations using the S32K3XX Microcontroller in an automotive system. It covers the most important topics such as the power considerations, Bulk/Bypass and decupling capacitors required, reset, crystal, Ethernet and QSPI configurations. Some PCB Layout recommendations are also provided.

### 2 Power System

Subsequent sections describe the different options for power supply configurations, as well as considerations to have for a proper connection of supply and ground pins.

# 2.1 S32K3XX Power Domains and Configurations

The S32K389 437MBGA, S32K388 , S32K358 – 289MBGA and 172HDQFP+EP, S32K344/24/14 - 257MBGA, S32K344/42/24/22/14 - 172HDQFP and S32K342/22 – 100HDQFP versions have two important and flexible power domains, VDD\_HV\_A, VREFH and VDD\_HV\_B that must be supplied externally at the same or different voltage level if in the application is required, and a V15 domain to +1.5V that can be supplied using an external NPN ballast transistor or externally supplied by an SBC. The S32K312-172HDQFP and the S32K314 /12 /11-100HDQFP versions have just a single power domain, VDD\_HV\_A. This VDD\_HV\_A reference will be the voltage domain for their IOs pins.

In the Table 1 is shown all positive power pins and domains that must be supplied externally and the internal MCU references.

| 1  | Introduction                                                                            |     |

|----|-----------------------------------------------------------------------------------------|-----|

| 2  | Power System                                                                            |     |

|    | 2.1 S32K3XX Power Domains and Configurations                                            |     |

|    | 2.2 VDD_HV_A - Main I/O and Analog Supply Voltage                                       |     |

|    | 2.3 VREFH – ADC High Reference Voltage                                                  |     |

|    | 2.4 VDD_HV_B - Secondary I/O Supply Voltage                                             | .3  |

|    | 2.5 V11 - Core logic voltage supply (+1.1 V)                                            | .3  |

|    | 2.6 V25 - Flash memory supply (+2.5 V)                                                  | .3  |

|    | 2.7 V15 - High-current logic supply voltage (+1.5V)                                     |     |

|    | <ul><li>2.8 VSS, VSS_DCDC and VREFL – Ground and ADC Reference</li><li>Low 44</li></ul> | nce |

|    | 2.9 Bulk and decoupling capacitors                                                      | .4  |

|    | 2.10 Power considerations                                                               |     |

|    | 2.11 Pinout differences between \$32K344/42/24/22/14                                    |     |

|    | 172HDQFP and S32K312-172HDQFP                                                           | .49 |

|    | 2.12 Pinout differences between S32K342/22-100HDQFP a                                   |     |

|    | S32K312/11-100HDQFP                                                                     |     |

|    | S32K388-MapBGA289                                                                       |     |

| 3  | Clock circuitry                                                                         |     |

| 3  | •                                                                                       |     |

|    | 3.1 EXTAL and XTAL pins                                                                 | .5  |

|    | 3.2 Suggestions for the PCB layout of oscillator circuit                                |     |

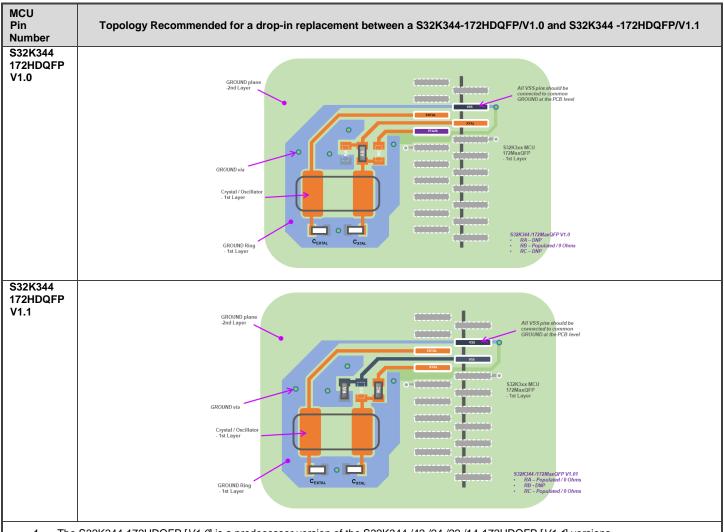

|    | 3.3 Pinout differences between S32K344-172HDQFP V1.0 a                                  |     |

|    | S32K344-172HDQFP V1.1                                                                   |     |

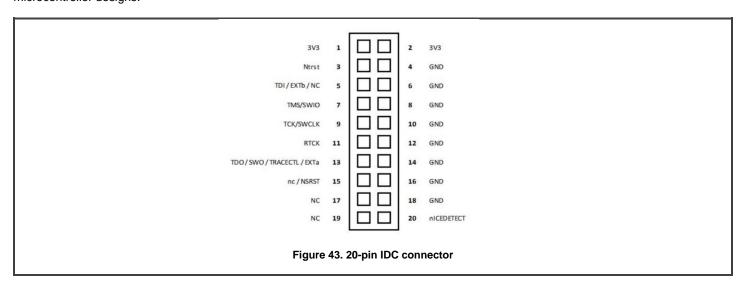

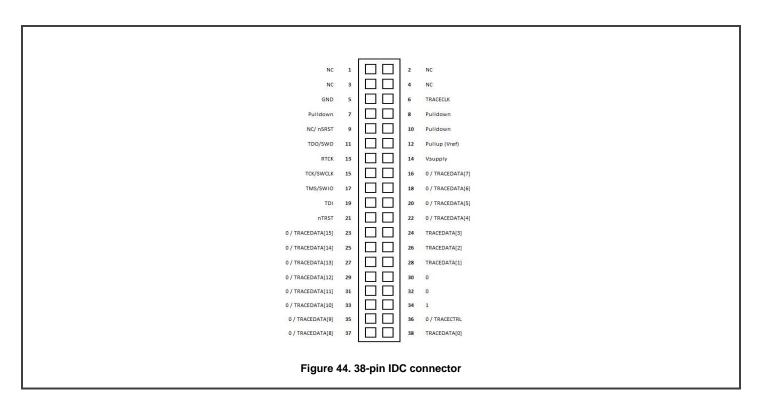

| 4  | Debug and programing interface                                                          | .6  |

|    | 4.1 RESET system                                                                        | 6   |

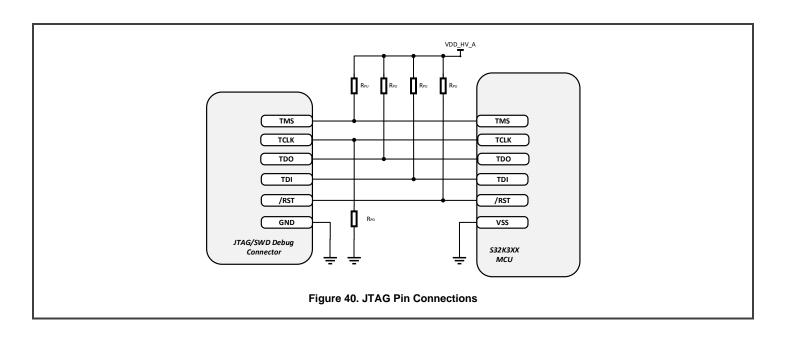

|    | 4.2 JTAG and TRACE interface                                                            |     |

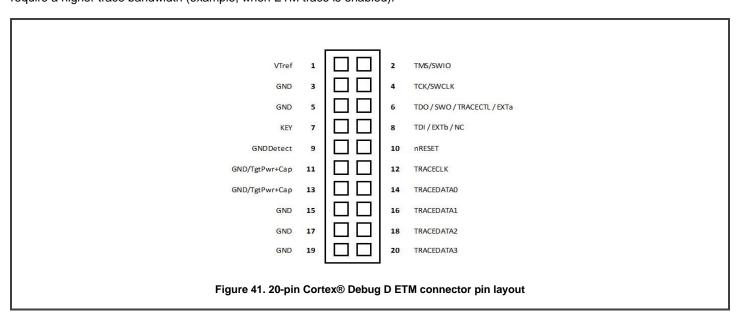

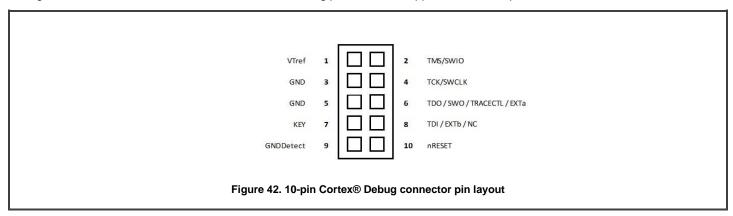

|    | 4.3 Debug connector pinouts                                                             |     |

| 5  | Communication modules                                                                   |     |

|    | E.A. LINI intenfere                                                                     | ٥.  |

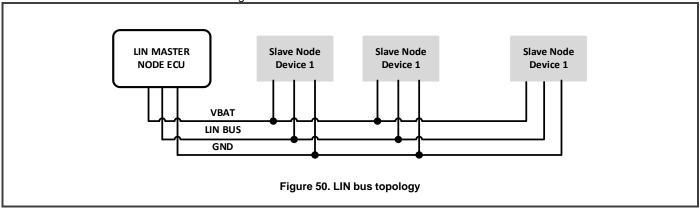

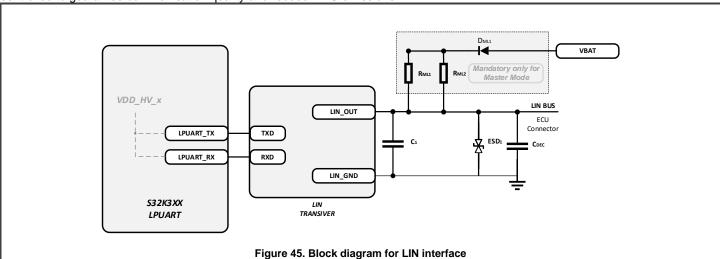

|    | 5.1 LIN interface                                                                       |     |

|    | 5.2 CAN interface                                                                       |     |

| 6  | Quad Serial Peripheral Interface                                                        |     |

| Ü  | •                                                                                       |     |

| 7  | Unused pins                                                                             |     |

| 8  | General board layout guidelines                                                         | .78 |

|    | 8.1 Traces recommendations                                                              | .78 |

|    | 8.2 Grounding                                                                           | .78 |

|    | 8.3 EMI/EMC and ESD considerations for layout                                           | .79 |

| 9  | CAD/CAE Schematic Symbols and PCB Footprints                                            | 8   |

| 10 | Package drawings                                                                        | .8  |

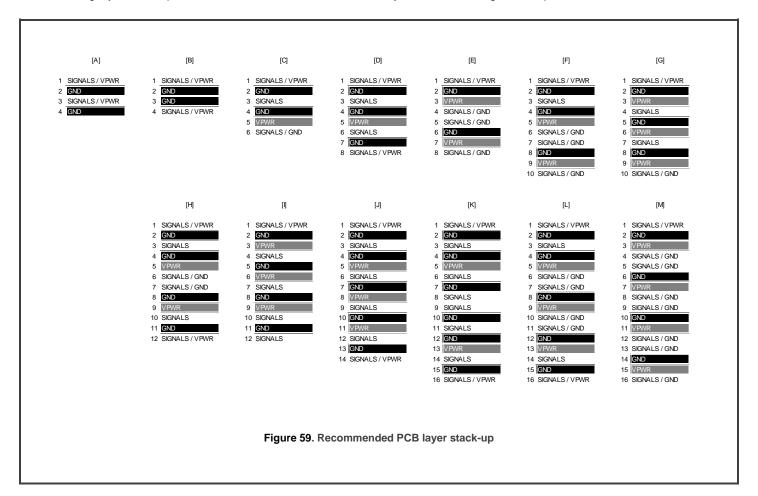

| 11 | PCB stackup design                                                                      | .8  |

| 12 | Injection current                                                                       | .8  |

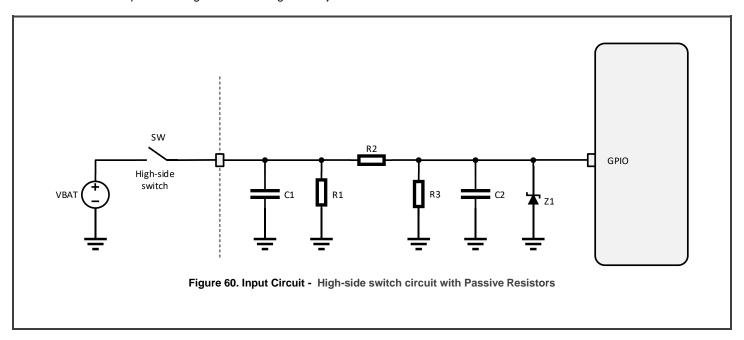

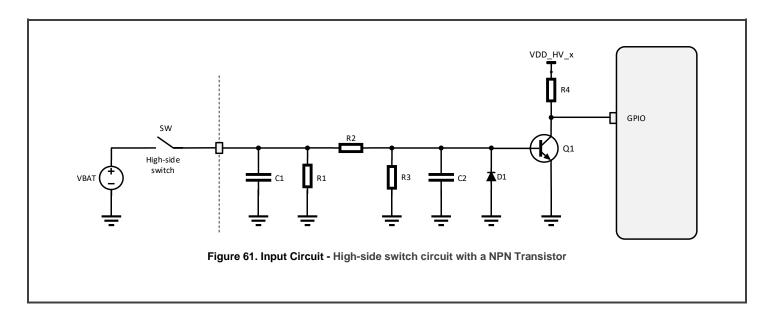

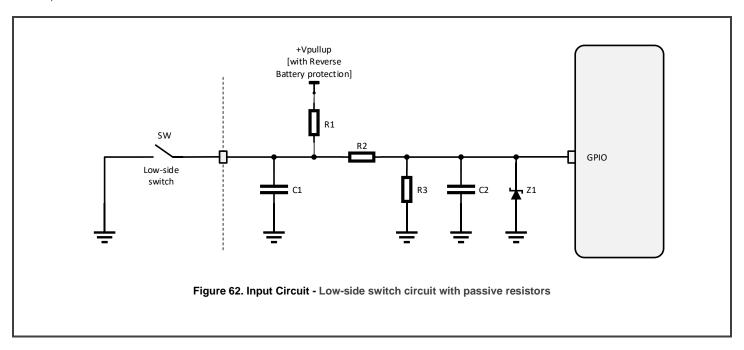

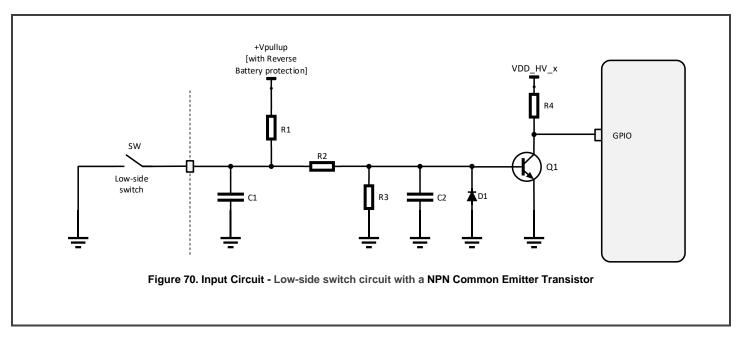

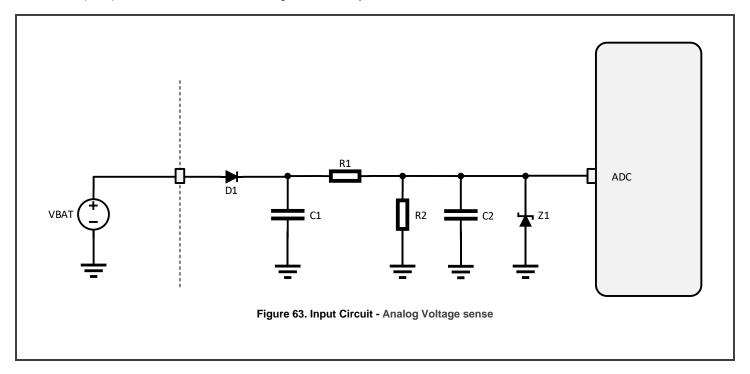

|    | 12.1 Input circuits for automotive applications                                         | 8   |

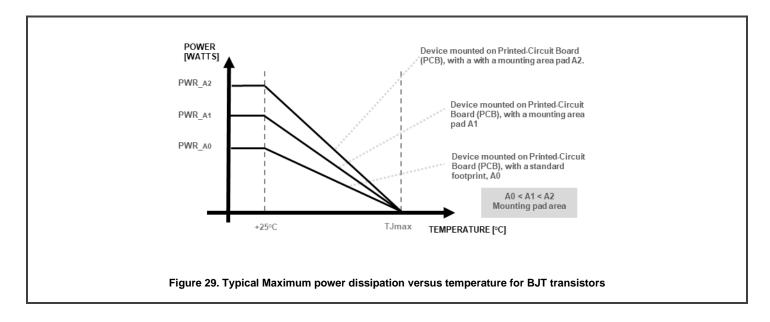

| 13 | Thermal                                                                                 |     |

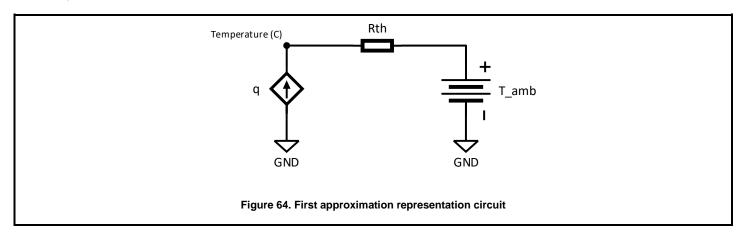

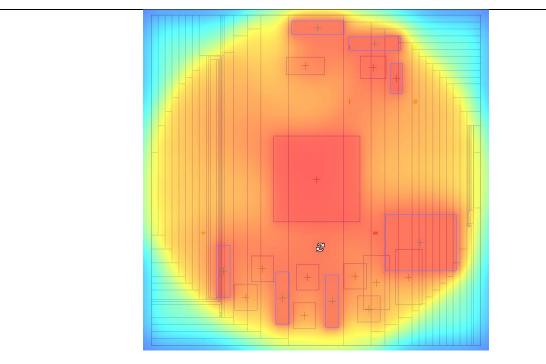

|    | 13.1 First Approximation                                                                | δ.  |

|    | 13.2 Heat spreading on a plate                                                          |     |

|    | 13.3 Complete System Calculation                                                        |     |

|    | 13.4 S32K38x Last Mile Regulator Calculation                                            |     |

| 14 | References                                                                              |     |

|    |                                                                                         |     |

| 15 | Revision history                                                                        | 9   |

Table 1. S32K3XX - Power supply pins and domains

|                                                                                    |                                 |                                            |                                  | Power supply pins                          | and domains              |                              |                                                                |

|------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------|----------------------------------|--------------------------------------------|--------------------------|------------------------------|----------------------------------------------------------------|

| S32K3<br>MCU                                                                       | MCU                             | VDD_HV_A                                   | VREFH                            | VDD_HV_B                                   | V15                      | V25                          | V11                                                            |

| version                                                                            | Package                         | +3.3V or<br>+5.0V <sup>[1]</sup>           | ≤ VDD_HV_A                       | +3.3V or +5.0V <sup>[1]</sup>              | +1.5V [1]                | +2.5V                        | +1.1V                                                          |

| S32K389                                                                            | 437<br>BGA                      | Domain and<br>Ref. voltage<br>for I/O pins | ADC High<br>Reference<br>Voltage | Domain and<br>Ref. voltage<br>for I/O pins | Power<br>Supply<br>Input | Internal<br>MCU<br>Reference | Power<br>Supply<br>Input –<br>regulated<br>by external<br>NMOS |

| S32K388                                                                            | 289<br>MBGA                     | Domain and<br>Ref. voltage<br>for I/O pins | ADC High<br>Reference<br>Voltage | Domain and<br>Ref. voltage<br>for I/O pins | Power<br>Supply<br>Input | Internal<br>MCU<br>Reference | Power<br>Supply<br>Input –<br>regulated<br>by external<br>NMOS |

| S32K328<br>S32K338<br>S32K348                                                      | 289<br>MBGA                     | Domain and<br>Ref. voltage<br>for I/O pins | ADC High<br>Reference<br>Voltage | Domain and<br>Ref. voltage<br>for I/O pins | Power<br>Supply<br>Input | Internal<br>MCU<br>Reference | Internal<br>MCU<br>Reference                                   |

| S32K358                                                                            | 172<br>HDQFP<br>+Exposed<br>Pad |                                            | voltage                          | TOT WE PINS                                | При                      | Neierenee                    | Reference                                                      |

| S32K344<br>S32K324<br>S32K314                                                      | 257<br>MBGA                     | Domain and<br>Ref. voltage<br>for I/O pins | ADC High<br>Reference<br>Voltage | Domain and<br>Ref. voltage<br>for I/O pins | Power<br>Supply<br>Input | Internal<br>MCU<br>Reference | Internal<br>MCU<br>Reference                                   |

| \$32K344 [V1.1]<br>\$32K344 [V1.0]<br>\$32K342<br>\$32K324<br>\$32K322<br>\$32K314 | 172<br>HDQFP                    |                                            |                                  |                                            |                          |                              |                                                                |

| S32K342<br>S32K322                                                                 | 100<br>HDQFP                    |                                            |                                  |                                            |                          |                              |                                                                |

| S32K312                                                                            | 172<br>HDQFP                    | Domain and<br>Ref. voltage                 | ADC High<br>Reference            | NA                                         | NA                       | Internal<br>MCU              | Internal<br>MCU                                                |

| S32K312<br>S32K311                                                                 | 100<br>HDQFP                    | for I/O pins                               | Voltage                          |                                            |                          | Reference                    | Reference                                                      |

| S32K311                                                                            | 48<br>LQFP                      | Domain and<br>Ref. voltage<br>for I/O pins | ADC High<br>Reference<br>Voltage | NA                                         | NA                       | Internal<br>MCU<br>Reference | Internal<br>MCU<br>Reference                                   |

| [1] Normal Operatio                                                                | n Voltage                       | 1                                          | 1                                |                                            |                          |                              |                                                                |

Application Note 2 / 93

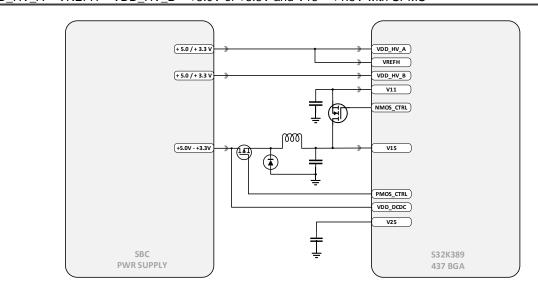

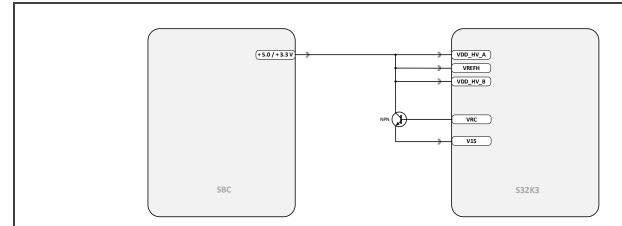

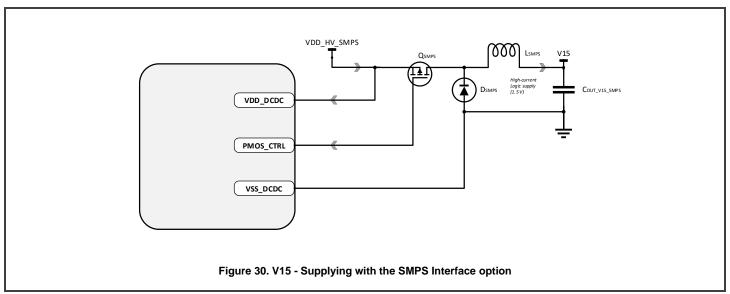

• VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V and V15 = +1.5V with SPMS

Figure 1. Block Diagram - VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V, and V15 = +1.5V with SMPS. MCU Power Configuration for S32K389 – 437MBGA

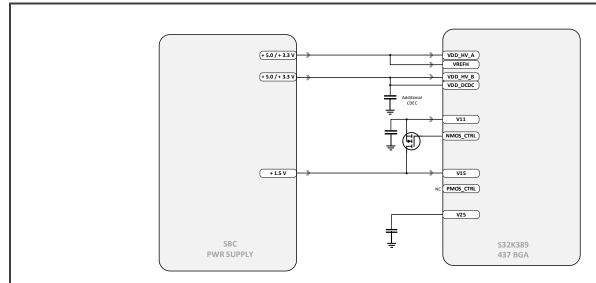

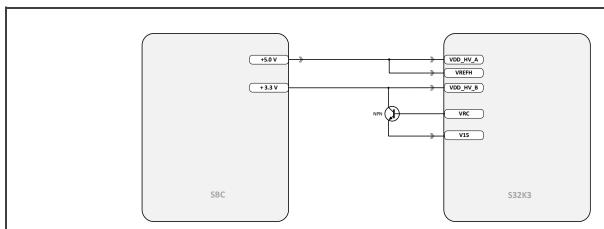

VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V and V15 = +1.5V by SBC

Figure 2. Block Diagram - VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V, and V15 = + 1.5V by SBC. MCU Power Configuration for S32K389 - 437MBGA

Application Note 3/93

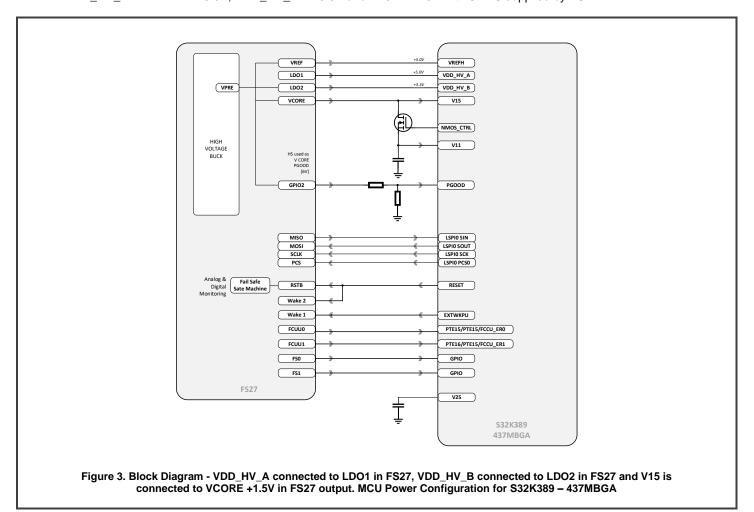

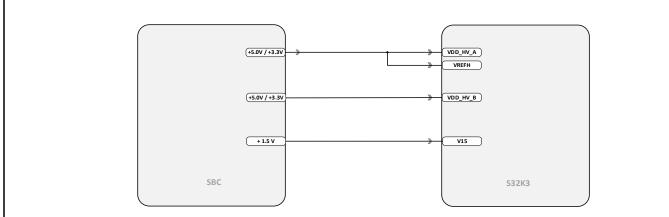

VDD\_HV\_A = VREFH = +5.0V, VDD\_HV\_B = +3.3V and V15 = + 1.5V with SMPS supplied by FS27

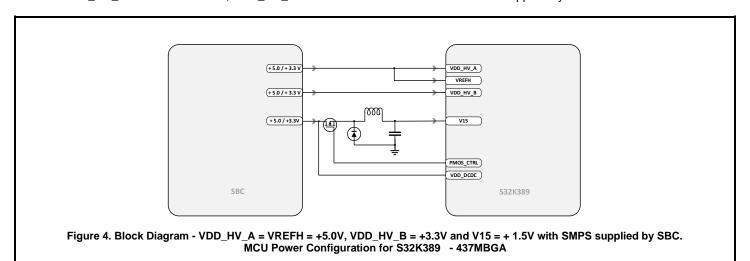

VDD\_HV\_A = VREFH = +5.0V, VDD\_HV\_B = +3.3V and V15 = + 1.5V with SMPS supplied by SBC

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 4 / 93

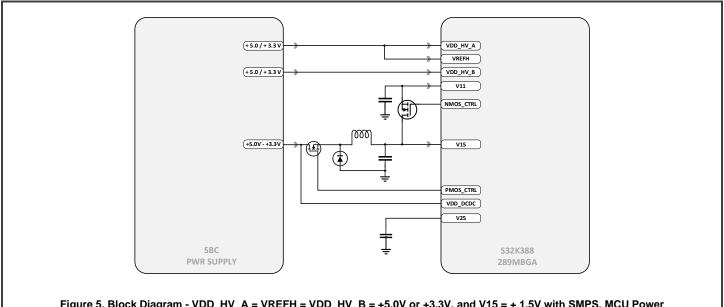

VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V and V15 = +1.5V with SPMS

Figure 5. Block Diagram - VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V, and V15 = + 1.5V with SMPS. MCU Power Configuration for S32K388 - 289MBGA

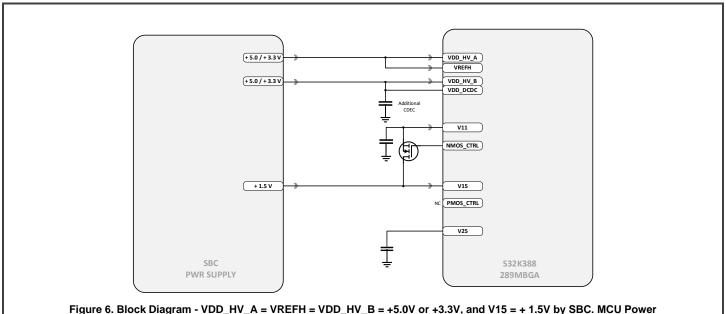

VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V and V15 = +1.5V by SBC

Figure 6. Block Diagram - VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V, and V15 = + 1.5V by SBC. MCU Power Configuration for S32K388 - 289MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 5 / 93

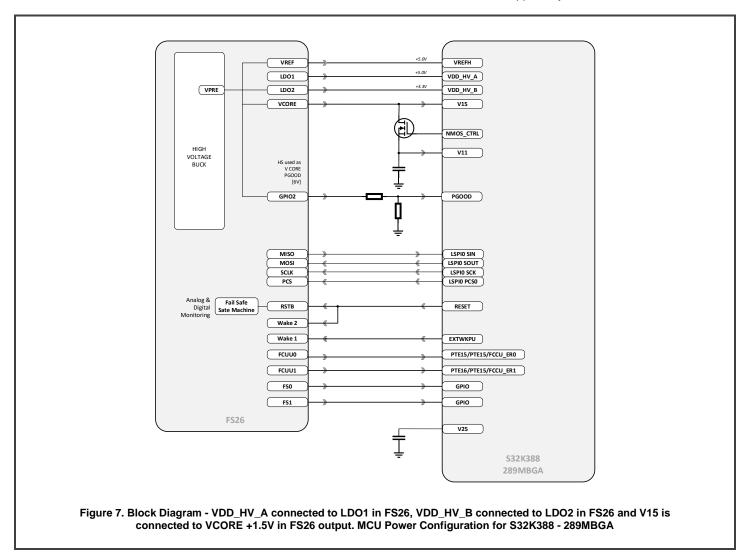

VDD\_HV\_A = VREFH = +5.0V, VDD\_HV\_B = +3.3V and V15 = + 1.5V with SMPS supplied by FS26

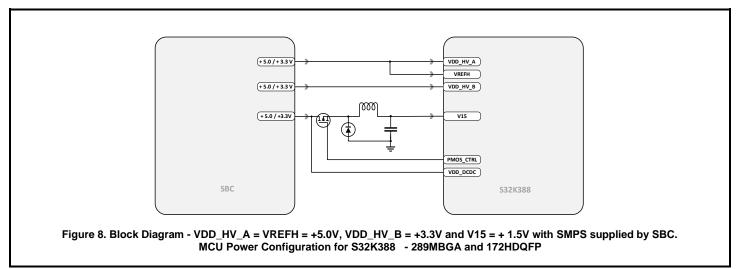

VDD\_HV\_A = VREFH = +5.0V, VDD\_HV\_B = +3.3V and V15 = +1.5V with SMPS supplied by SBC

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 6 / 93

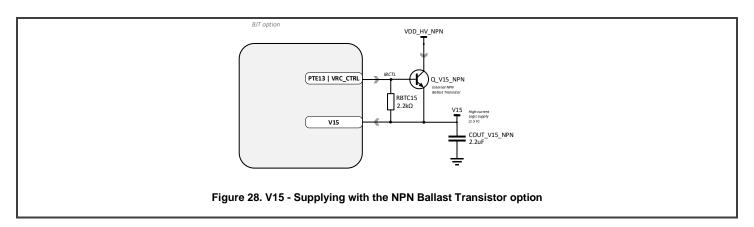

VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V and V15 = +1.5V with external NPN Ballast Transistor

Figure 9. Block Diagram - VDD\_HV\_A = VREFH = VDD\_HV\_B = +5.0V or +3.3V, and V15 = +1.5V with external NPN Ballast Transistor. MCU Power Configuration for S32K344/24/14 - 257MBGA, S32K344/42/24/22/14 - 172HDQFP and S32K342/22 – 100HDQFP

VDD\_HV\_A = VREFH = +5.0V and VDD\_HV\_B = +3.3V and V15 = +1.5V with external NPN Ballast Transistor

Figure 10. Block Diagram - VDD\_HV\_A = VREFH = +5.0V and VDD\_HV\_B = +3.3V and V15 = +1.5V with external NPN Ballast Transistor - MCU Power Configuration for S32K344/24/14 - 257MBGA, S32K344/42/24/22/14 - 172HDQFP, S32K342/22 - 100HDQFP and S32K358 - 289 MBGA/172HDQFP

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 7 / 93

VDD\_HV\_A = VREFH = +5.0V and VDD\_HV\_B = +3.3V and V15 = +1.5V

Figure 11. Block Diagram - VDD\_HV\_A = VREFH = +5.0V and VDD\_HV\_B = +3.3V and V15 = +1.5V - MCU Power Configuration for S32K344/24/14 - 257MBGA, S32K344/42/24/22/14 - 172HDQFP, S32K342/22 - 100HDQFP and S32K358 - 289MBGA/172HDQFP

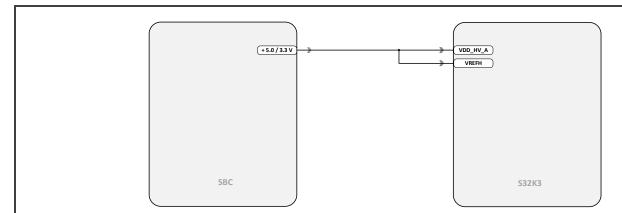

For the S32K312 - 172HDQFP and the S32K312/11 - 100HDQFP, just the VDD\_HV\_A domain and VREFH are presented.

VDD\_HV\_A = VREFH = +5.0V or +3.3V

Figure 12. Block Diagram - VDD\_HV\_A = VREFH = +5.0V. MCU Power Configuration for S32K312 - 172HDQFP, S32K314/12/11 - 100HDQFP and S32K311 - 48LQFP

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 8 / 93

#### 2.1.1 General view of the pinout and power domains for the S32K3 MCU family

In this section is shown an overview of the voltage domains for the different interfaces and I/Os in the MCU. Please refer to the latest version of the *Datasheet* and *S32K3XX\_IO\_Signal\_Description File* for more details.

#### 2.1.1.1 General view of the pinout and power domains for the S32K389 – 437MapBGA Package

|    | 1       | 2            | 3     | 4     | 5     | 6            | 7            | 8     | 9            | 10           | 11      | 12           | 13           | 14    | 15           | 16           | 17    | 18    | 19           | 20           | 21    | 1  |

|----|---------|--------------|-------|-------|-------|--------------|--------------|-------|--------------|--------------|---------|--------------|--------------|-------|--------------|--------------|-------|-------|--------------|--------------|-------|----|

| Α  |         | PTH13        | PTH14 | PTH15 | PTH16 | PTH17        | PTH18        | PTH19 | PTH20        | PTH21        | PTH22   | PTH23        | PTH24        | PTH26 | PTH25        | VSS          | PTH27 | PTH28 | PTH29        | VSS          |       | Α  |

| В  | PTIO    | VSS          | V11   | РТНЗО | PTH31 | VDD_HV_<br>A | VSS          | V11   | PTI8         | V11          | VSS     | VDD_HV_<br>A | PTI9         | PTI10 | PTI11        | V11          | PTI12 | PTI13 | VDD_HV_<br>A | VSS          | PTI14 | В  |

| С  | PTI1    | VDD_HV_<br>A | PTG10 | PTA8  | PTA5  | PTE30        | PTE1         | PTFO  | PTA12        | PTE24        | PTA13   | PTA14        | PTA15        | PTA16 | PTAO         | PTB8         | PTD27 | PTD26 | PTG11        | V11          | PTI15 | С  |

| D  | PTI2    | PTI6         | PTA18 | VSS   | PTA9  | PTE31        | PTEO         | PTF1  | PTA11        | PTE25        | PTE22   | PTE2         | PTE6         | PTC7  | PTD28        | PTA1         | PTF9  | VSS   | PTF10        | PTI16        | PTI17 | D  |

| Е  | NMOS_CT | vss          | PTA19 | PTE16 | PTA22 | PTE28        | PTE29        | PTF2  | PTF4         | PTF5         | PTF7    | PTE20        | PTE19        | PTC6  | PTD31        | PTD29        | PTB9  | PTD25 | PTB11        | VDD_HV_<br>A | PTI21 | E  |

| F  | VSS     | VSS          | PTA21 | PTE15 | PTA23 | vss          | PTE26        | PTF3  | PTF6         | PTE23        | VSS     | PTF8         | PTE18        | PTE17 | PTD30        | VDD_HV_<br>A | PTB10 | PTD24 | PTA2         | VSS          | PTI19 | F  |

| G  | PTA24   | vss          | PTE11 | PTE10 | PTD1  | PTA20        | VDD_HV_<br>A | PTG31 | РТНО         | PTH1         | V11     | PTH2         | РТНЗ         | PTH4  | VSS          | PTF13        | PTF12 | PTA3  | PTD23        | V11          | PTI18 | G  |

| н  | PTA25   | vss          | PTJ1  | PTES  | PTDO  | PTG8         | PTG30        | PTA4  | PTC4         | PTC5         | PTE21   | PTG27        | PTG26        | PTG25 | PTH5         | PTF15        | PTF14 | PTD2  | PTD3         | PTI22        | PTI20 | н  |

| J  | VSS     | VSS          | VSS   | PTG9  | PTG13 | PTG4         | PTG29        | PTE4  | vss          | PTA10        | PTE27   | VDD_HV_<br>A | VSS          | PTG24 | РТН6         | PTF17        | PTF16 | PTD4  | PTD22        | PTI23        | VSS   | J  |

| К  | EXTAL   | vss          | VSS   | PTG1  | PTG14 | PTG5         | PTG28        | VREFH | VDD_HV_<br>A | V15          | V11     | V11          | PTF11        | PTG23 | VDD_HV_<br>A | PTF18        | PTD21 | PTB13 | PTB12        | PTI24        | PTI25 | К  |

| L  | XTAL    | VSS          | VSS   | PTGO  | PTG2  | VSS          | VSS_DCD<br>C | VREFL | V25          | V11          | VSS     | V11          | PTF19        | PTG22 | V11          | VSS          | PTF20 | PTB15 | PTB14        | VDD_HV_<br>A | PTI26 | L  |

| М  | VSS     | VSS          | PTI5  | PTG3  | PTF30 | PTF29        | PMOS_CT      | PTG7  | PTG6         | V11          | V11     | V11          | VDD_HV_<br>A | PTG21 | PTH7         | PTF21        | PTD20 | PTB17 | PTB16        | VSS          | PTI27 | М  |

| N  | PTI3    | V11          | PTJO  | PTA26 | PTE14 | PTD15        | VDD_DCD<br>C | PTG15 | vss          | VDD_HV_<br>A | PTF31   | PTF28        | VSS          | PTG20 | PTH8         | PTC31        | PTD19 | PTD18 | PTA17        | V11          | PTI29 | N  |

| Р  | PTI4    | PTI7         | PTE12 | PTA27 | PTA29 | PTD14        | VSS          | PTB22 | PTB23        | PTG16        | PTG17   | PTG18        | PTG19        | PTF24 | РТН9         | PTF23        | PTA6  | PTA7  | PTE7         | PTI28        | PTI30 | Р  |

| R  | PTJ4    | V11          | PTE3  | PTA28 | PTD17 | VDD_HV_      | VDD_HV_<br>A | V11   | VSS          | V11          | VDD_HV_ | VSS          | PTH12        | PTH11 | PTH10        | PTC9         | PTC8  | PTC29 | PTC30        | PTJ8         | PTI31 | R  |

| Т  | PTJ5    | VSS          | PTA31 | PTD16 | PTA30 | VSS          | PTD13        | PTC16 | PTB24        | PTB25        | PTB27   | PTB28        | PTC12        | PTF25 | PTF27        | VSS          | PTC26 | РТВО  | PTC28        | V11          | РТЈ9  | Т  |

| U  | PTJ6    | VDD_HV_      | PTB18 | PTB19 | PTE9  | PTE8         | PTD12        | PTC17 | VDD_HV_      | PTD8         | PTB26   | VDD_HV_      | PTC13        | PTF26 | PTC21        | PTC25        | PTC24 | PTC27 | PTB1         | VSS          | PTJ10 | U  |

| v  | PTJ7    | VSS          | PTB20 | VSS   | PTC3  | PTC2         | PTD6         | PTD10 | vss          | PTC1         | PTC14   | VSS          | PTB2         | PTC19 | PTC20        | PTB31        | PTC11 | vss   | PTC10        | VDD_HV_<br>A | PTJ11 | v  |

| w  | PTJ2    | V11          | PTB21 | PTB5  | PTB4  | PTD7         | PTD5         | PTD11 | PTCO         | PTD9         | PTC15   | PTB3         | PTC18        | PTB29 | PTB30        | PTC23        | PTC22 | PTF22 | PTG12        | PTJ13        | PTJ12 | w  |

| Υ  | PTJ3    | VSS          | РТКО  | V11   | VSS   | VDD_HV_      | PTJ30        | V11   | VSS          | VDD_HV_<br>B | PTJ24   | V11          | VSS          | PTJ22 | VDD_HV_<br>A | VSS          | V11   | PTJ16 | VDD_HV_      | VSS          | PTJ14 | Υ  |

| AA |         | VSS          | PTK1  | PTK2  | PTK3  | PTJ31        | PTJ29        | PTJ28 | PTJ23        | PTJ26        | VSS     | PTJ27        | PTJ25        | PTJ21 | PTJ20        | PTJ19        | PTJ18 | PTJ17 | VSS          | PTJ15        |       | AA |

|    | 1       | 2            | 3     | 4     | 5     | 6            | 7            | 8     | 9            | 10           | 11      | 12           | 13           | 14    | 15           | 16           | 17    | 18    | 19           | 20           | 21    | J  |

| MCU Pin Function                                                        | #Pins |

|-------------------------------------------------------------------------|-------|

| VDD_HV_A and VREFH Power Pin                                            | 19    |

| I/Os pins on the VDD_HV_A Power Domain [including JTAG(4) and RESET(1)] | 251   |

| VDD_HV_B Power Pin                                                      | 6     |

| I/Os pins on the VDD_HV_B Power Domain                                  | 70    |

| XTAL/EXTAL                                                              | 2     |

| V25 Power Pin                                                           | 1     |

| V15 Power Pin                                                           | 1     |

| SMPS Interface for V15                                                  | 2     |

| V11 Power Pin [including NMOS_CTRL]                                     | 27    |

| VSSx and VREFL – Ground pin                                             | 58    |

| TOTAL of pins                                                           | 437   |

Figure 5. General view of the pinout and power domains for the S32K389 - 437MapBGA Package

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 9 / 93

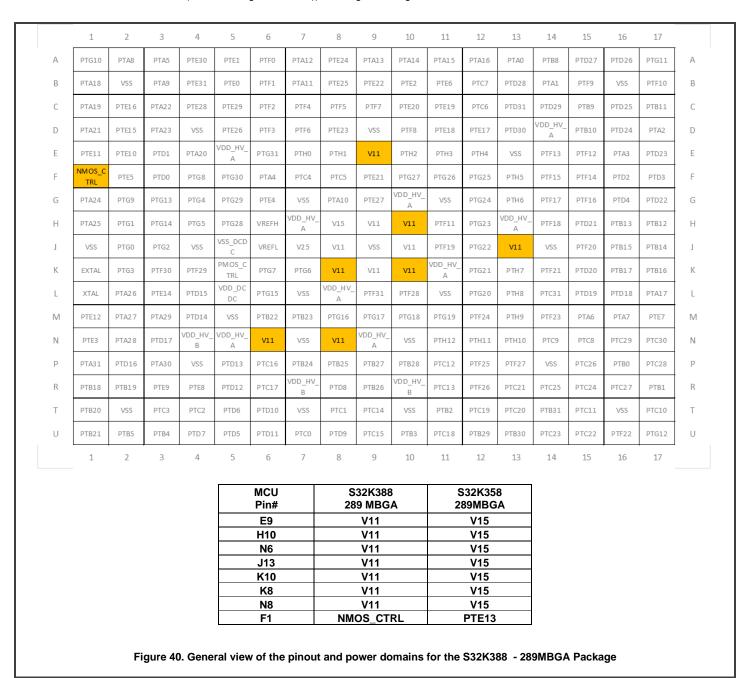

# 2.1.1.2 General view of the pinout and power domains for the S32K388 - 289MapBGA Package

|   | 1             | 2     | 3     | 4           | 5             | 6     | 7           | 8           | 9           | 10          | 11          | 12    | 13           | 14          | 15    | 16    | 17    |   |

|---|---------------|-------|-------|-------------|---------------|-------|-------------|-------------|-------------|-------------|-------------|-------|--------------|-------------|-------|-------|-------|---|

| Α | PTG10         | PTA8  | PTA5  | PTE30       | PTE1          | PTF0  | PTA12       | PTE24       | PTA13       | PTA14       | PTA15       | PTA16 | PTA0         | PTB8        | PTD27 | PTD26 | PTG11 | А |

| В | PTA18         | VSS   | PTA9  | PTE31       | PTEO          | PTF1  | PTA11       | PTE25       | PTE22       | PTE2        | PTE6        | PTC7  | PTD28        | PTA1        | PTF9  | vss   | PTF10 | В |

| С | PTA19         | PTE16 | PTA22 | PTE28       | PTE29         | PTF2  | PTF4        | PTF5        | PTF7        | PTE20       | PTE19       | PTC6  | PTD31        | PTD29       | PTB9  | PTD25 | PTB11 | С |

| D | PTA21         | PTE15 | PTA23 | VSS         | PTE26         | PTF3  | PTF6        | PTE23       | VSS         | PTF8        | PTE18       | PTE17 | PTD30        | VDD_HV<br>A | PTB10 | PTD24 | PTA2  | D |

| E | PTE11         | PTE10 | PTD1  | PTA20       | VDD_HV<br>A   | PTG31 | PTH0        | PTH1        | V11         | PTH2        | PTH3        | PTH4  | VSS          | PTF13       | PTF12 | PTA3  | PTD23 | E |

| F | NMOS_C<br>TRL | PTE5  | PTD0  | PTG8        | PTG30         | PTA4  | PTC4        | PTC5        | PTE21       | PTG27       | PTG26       | PTG25 | PTH5         | PTF15       | PTF14 | PTD2  | PTD3  | F |

| G | PTA24         | PTG9  | PTG13 | PTG4        | PTG29         | PTE4  | VSS         | PTA10       | PTE27       | VDD_HV<br>A | VSS         | PTG24 | PTH6         | PTF17       | PTF16 | PTD4  | PTD22 | G |

| Н | PTA25         | PTG1  | PTG14 | PTG5        | PTG28         | VREFH | VDD_HV<br>A | V15         | V11         | V11         | PTF11       | PTG23 | VDD_HV<br>_A | PTF18       | PTD21 | PTB13 | PTB12 | н |

| J | VSS           | PTG0  | PTG2  | VSS         | VSS_DCD<br>C  | VSS   | V25         | V11         | VSS         | V11         | PTF19       | PTG22 | V11          | VSS         | PTF20 | PTB15 | PTB14 | J |

| К | EXTAL         | PTG3  | PTF30 | PTF29       | PMOS_C<br>TRL | PTG7  | PTG6        | V11         | V11         | V11         | VDD_HV<br>A | PTG21 | PTH7         | PTF21       | PTD20 | PTB17 | PTB16 | К |

| L | XTAL          | PTA26 | PTE14 | PTD15       | VDD_DC<br>DC  | PTG15 | VSS         | VDD_HV<br>A | PTF31       | PTF28       | VSS         | PTG20 | PTH8         | PTC31       | PTD19 | PTD18 | PTA17 | L |

| М | PTE12         | PTA27 | PTA29 | PTD14       | VSS           | PTB22 | PTB23       | PTG16       | PTG17       | PTG18       | PTG19       | PTF24 | РТН9         | PTF23       | PTA6  | PTA7  | PTE7  | М |

| N | PTE3          | PTA28 | PTD17 | VDD_HV<br>B | VDD_HV<br>A   | V11   | VSS         | V11         | VDD_HV<br>A | VSS         | PTH12       | PTH11 | PTH10        | PTC9        | PTC8  | PTC29 | PTC30 | N |

| Р | PTA31         | PTD16 | PTA30 | VSS         | PTD13         | PTC16 | PTB24       | PTB25       | PTB27       | PTB28       | PTC12       | PTF25 | PTF27        | VSS         | PTC26 | PTB0  | PTC28 | Р |

| R | PTB18         | PTB19 | PTE9  | PTE8        | PTD12         | PTC17 | VDD_HV<br>B | PTD8        | PTB26       | VDD_HV<br>B | PTC13       | PTF26 | PTC21        | PTC25       | PTC24 | PTC27 | PTB1  | R |

| Т | PTB20         | VSS   | PTC3  | PTC2        | PTD6          | PTD10 | VSS         | PTC1        | PTC14       | VSS         | PTB2        | PTC19 | PTC20        | PTB31       | PTC11 | VSS   | PTC10 | Т |

| U | PTB21         | PTB5  | PTB4  | PTD7        | PTD5          | PTD11 | PTC0        | PTD9        | PTC15       | PTB3        | PTC18       | PTB29 | PTB30        | PTC23       | PTC22 | PTF22 | PTG12 | U |

|   | 1             | 2     | 3     | 4           | 5             | 6     | 7           | 8           | 9           | 10          | 11          | 12    | 13           | 14          | 15    | 16    | 17    |   |

| MCU Pin Function                       | #Pins           |

|----------------------------------------|-----------------|

| VDD_HV_A and VREFH Power Pin           | 10              |

| I/Os pins on the VDD_HV_A Power Domain | 182             |

| [including JTAG(4) and RESET(1)]       |                 |

| VDD_HV_B Power Pin                     | 3               |

| I/Os pins on the VDD_HV_B Power Domain | 52              |

| XTAL/EXTAL                             | 2               |

| V25 Power Pin                          | 1               |

| V15 Power Pin                          | 1               |

| SMPS Interface for V15                 | <del>2</del> -2 |

| V11 Power Pin [including NMOS_CTRL]    | 12              |

| VSSx and VREFL – Ground pin            | 24              |

| TOTAL of pin                           | s 289           |

Figure 6. General view of the pinout and power domains for the S32K388 - 289MapBGA Package

Application Note 10 / 93

# 2.1.1.3 General view of the pinout and power domains for the S32K358 - 289MapBGA Package

|   | 1     | 2     | 3     | 4            | 5             | 6     | 7            | 8            | 9            | 10           | 11           | 12    | 13           | 14           | 15    | 16    | 17    |   |

|---|-------|-------|-------|--------------|---------------|-------|--------------|--------------|--------------|--------------|--------------|-------|--------------|--------------|-------|-------|-------|---|

| Α | PTG10 | PTA8  | PTA5  | PTE30        | PTE1          | PTF0  | PTA12        | PTE24        | PTA13        | PTA14        | PTA15        | PTA16 | PTA0         | PTB8         | PTD27 | PTD26 | PTG11 | Α |

| В | PTA18 | VSS   | PTA9  | PTE31        | PTEO          | PTF1  | PTA11        | PTE25        | PTE22        | PTE2         | PTE6         | PTC7  | PTD28        | PTA1         | PTF9  | VSS   | PTF10 | В |

| С | PTA19 | PTE16 | PTA22 | PTE28        | PTE29         | PTF2  | PTF4         | PTF5         | PTF7         | PTE20        | PTE19        | PTC6  | PTD31        | PTD29        | PTB9  | PTD25 | PTB11 | С |

| D | PTA21 | PTE15 | PTA23 | VSS          | PTE26         | PTF3  | PTF6         | PTE23        | VSS          | PTF8         | PTE18        | PTE17 | PTD30        | VDD_HV_<br>A | PTB10 | PTD24 | PTA2  | D |

| Е | PTE11 | PTE10 | PTD1  | PTA20        | VDD_HV_<br>A  | PTG31 | PTH0         | PTH1         | V15          | PTH2         | PTH3         | PTH4  | VSS          | PTF13        | PTF12 | PTA3  | PTD23 | E |

| F | PTE13 | PTE5  | PTD0  | PTG8         | PTG30         | PTA4  | PTC4         | PTC5         | PTE21        | PTG27        | PTG26        | PTG25 | PTH5         | PTF15        | PTF14 | PTD2  | PTD3  | F |

| G | PTA24 | PTG9  | PTG13 | PTG4         | PTG29         | PTE4  | VSS          | PTA10        | PTE27        | VDD_HV_<br>A | VSS          | PTG24 | PTH6         | PTF17        | PTF16 | PTD4  | PTD22 | G |

| Н | PTA25 | PTG1  | PTG14 | PTG5         | PTG28         | VREFH | VDD_HV_<br>A | V15          | V11          | V15          | PTF11        | PTG23 | VDD_HV_<br>A | PTF18        | PTD21 | PTB13 | PTB12 | Н |

| J | VSS   | PTG0  | PTG2  | VSS          | VSS_DCD<br>C  | VREFL | V25          | V11          | VSS          | V11          | PTF19        | PTG22 | V15          | VSS          | PTF20 | PTB15 | PTB14 | J |

| K | EXTAL | PTG3  | PTF30 | PTF29        | PMOS_C<br>TRL | PTG7  | PTG6         | V15          | V11          | V15          | VDD_HV_<br>A | PTG21 | PTH7         | PTF21        | PTD20 | PTB17 | PTB16 | К |

| L | XTAL  | PTA26 | PTE14 | PTD15        | VDD_DC<br>DC  | PTG15 | VSS          | VDD_HV_<br>A | PTF31        | PTF28        | VSS          | PTG20 | PTH8         | PTC31        | PTD19 | PTD18 | PTA17 | L |

| М | PTE12 | PTA27 | PTA29 | PTD14        | VSS           | PTB22 | PTB23        | PTG16        | PTG17        | PTG18        | PTG19        | PTF24 | PTH9         | PTF23        | PTA6  | PTA7  | PTE7  | М |

| N | PTE3  | PTA28 | PTD17 | VDD_HV_<br>B | VDD_HV_<br>A  | V15   | VSS          | V15          | VDD_HV_<br>A | VSS          | PTH12        | PTH11 | PTH10        | PTC9         | PTC8  | PTC29 | PTC30 | N |

| Р | PTA31 | PTD16 | PTA30 | VSS          | PTD13         | PTC16 | PTB24        | PTB25        | PTB27        | PTB28        | PTC12        | PTF25 | PTF27        | VSS          | PTC26 | PTB0  | PTC28 | Р |

| R | PTB18 | PTB19 | PTE9  | PTE8         | PTD12         | PTC17 | VDD_HV_<br>B | PTD8         | PTB26        | VDD_HV_<br>B | PTC13        | PTF26 | PTC21        | PTC25        | PTC24 | PTC27 | PTB1  | R |

| Т | PTB20 | VSS   | PTC3  | PTC2         | PTD6          | PTD10 | VSS          | PTC1         | PTC14        | VSS          | PTB2         | PTC19 | PTC20        | PTB31        | PTC11 | VSS   | PTC10 | Т |

| U | PTB21 | PTB5  | PTB4  | PTD7         | PTD5          | PTD11 | PTC0         | PTD9         | PTC15        | PTB3         | PTC18        | PTB29 | PTB30        | PTC23        | PTC22 | PTF22 | PTG12 | U |

|   | 1     | 2     | 3     | 4            | 5             | 6     | 7            | 8            | 9            | 10           | 11           | 12    | 13           | 14           | 15    | 16    | 17    |   |

| MCU Pin Function                                                        | #Pins |

|-------------------------------------------------------------------------|-------|

| VDD_HV_A and VREFH Power Pin                                            | 10    |

| I/Os pins on the VDD_HV_A Power Domain [including JTAG(4) and RESET(1)] | 183   |

| VDD_HV_B Power Pin                                                      | 3     |

| I/Os pins on the VDD_HV_B Power Domain                                  | 52    |

| XTAL/EXTAL                                                              | 2     |

| V25 Power Pin                                                           | 1     |

| V15 Power Pin                                                           | 8     |

| SMPS Interface for V15                                                  | 2     |

| V11 Power Pin                                                           | 4     |

| VSSx and VREFL – Ground pin                                             | 24    |

| TOTAL of pins                                                           | 289   |

Figure 7. General view of the pinout and power domains for the S32K358 - 289MapBGA Package

Application Note 11 / 93

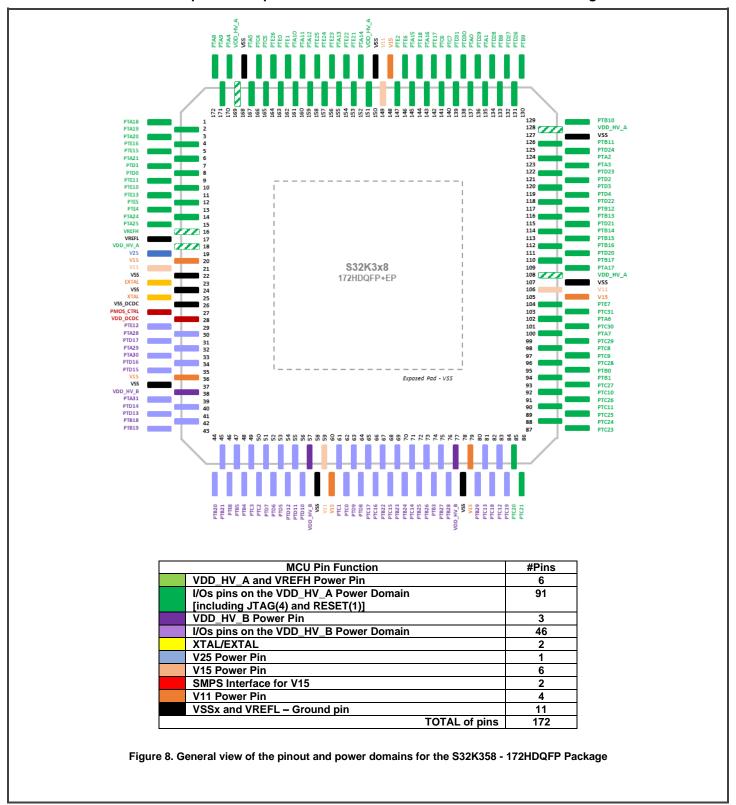

#### 2.1.1.4 General view of the pinout and power domains for the S32K358 - 172HDQFP Package

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 12 / 93

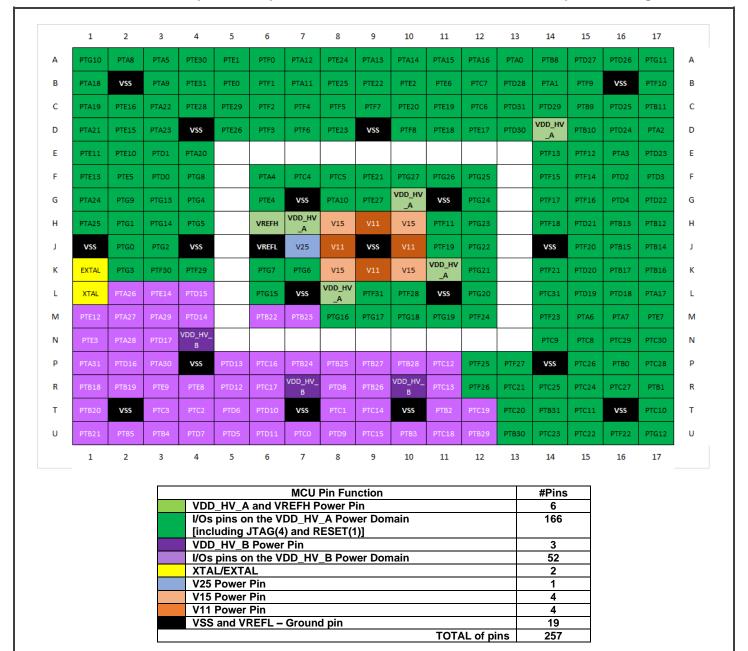

#### 2.1.1.5 General view of the pinout and power domains for the S32K344/24/14 - 257MapBGA Package

Figure 9. General view of the pinout and power domains for the S32K344/24/14 - 257MapBGA Package

Application Note 13 / 93

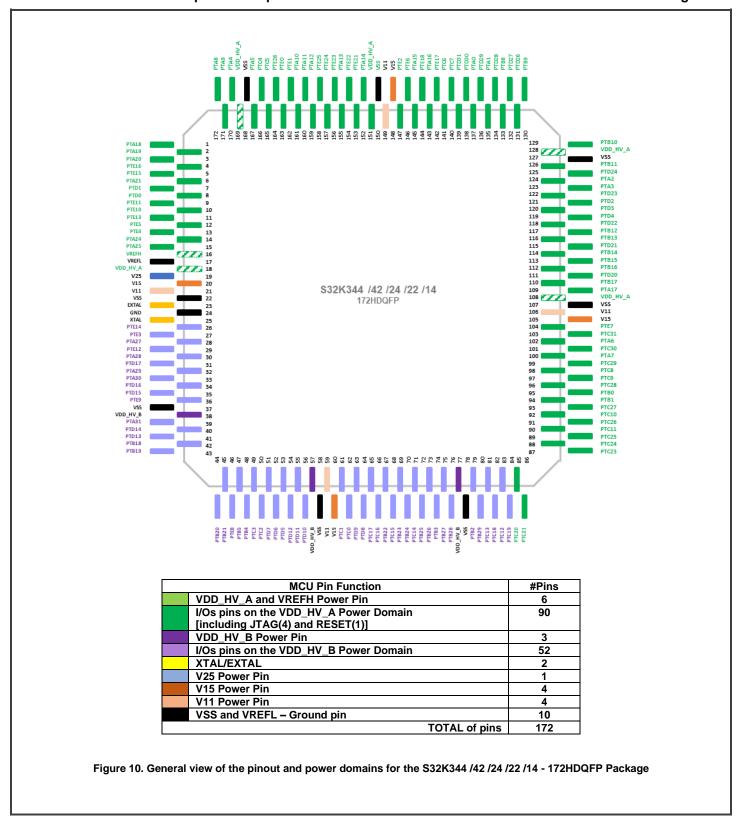

#### 2.1.1.6 General view of the pinout and power domains for the S32K344 /42 /24 /22 /14 - 172HDQFP Package

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 14 / 93

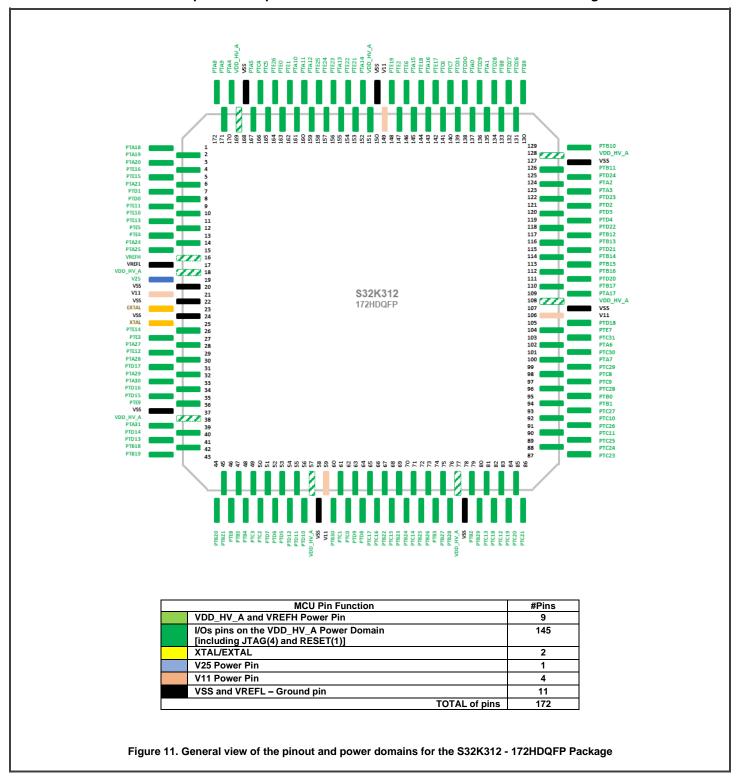

#### 2.1.1.7 General view of the pinout and power domains for the S32K312 - 172HDQFP Package

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 15 / 93

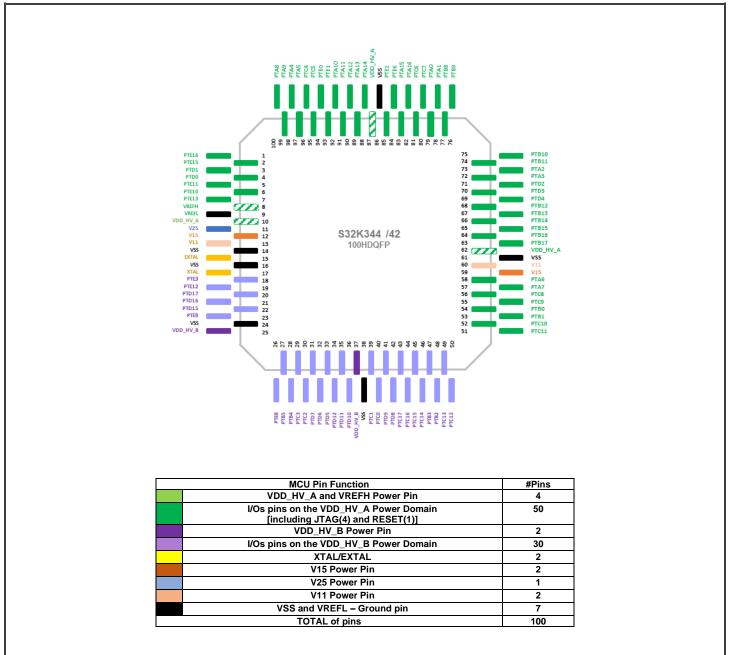

#### 2.1.1.8 General view of the pinout and power domains for the S32K342 /22 - 100HDQFP Package

Figure 12. General view of the pinout and power domains for the S32K342 /22 - 100HDQFP Package

Application Note 16 / 93

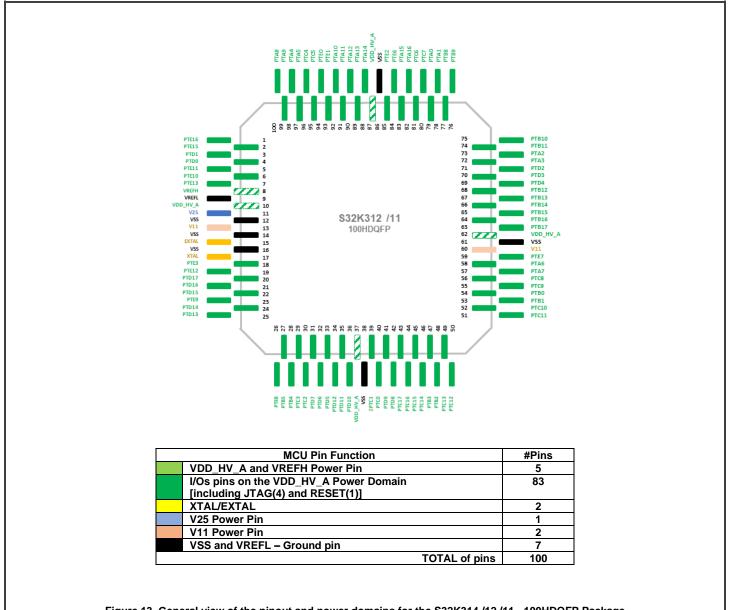

#### 2.1.1.9 General view of the pinout and power domains for the S32K314 /12 /11 - 100HDQFP Package

Figure 13. General view of the pinout and power domains for the S32K314 /12 /11 - 100HDQFP Package

Application Note 17 / 93

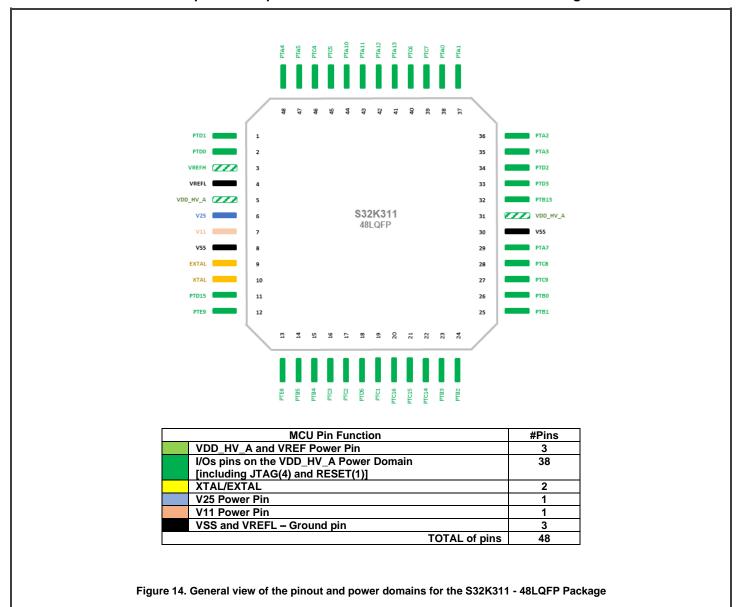

#### 2.1.1.10 General view of the pinout and power domains for the S32K311 - 48LQFP Package

Application Note 18 / 93

#### 2.1.2 Bulk/Bypass and decoupling capacitors scheme for the S32K3 family

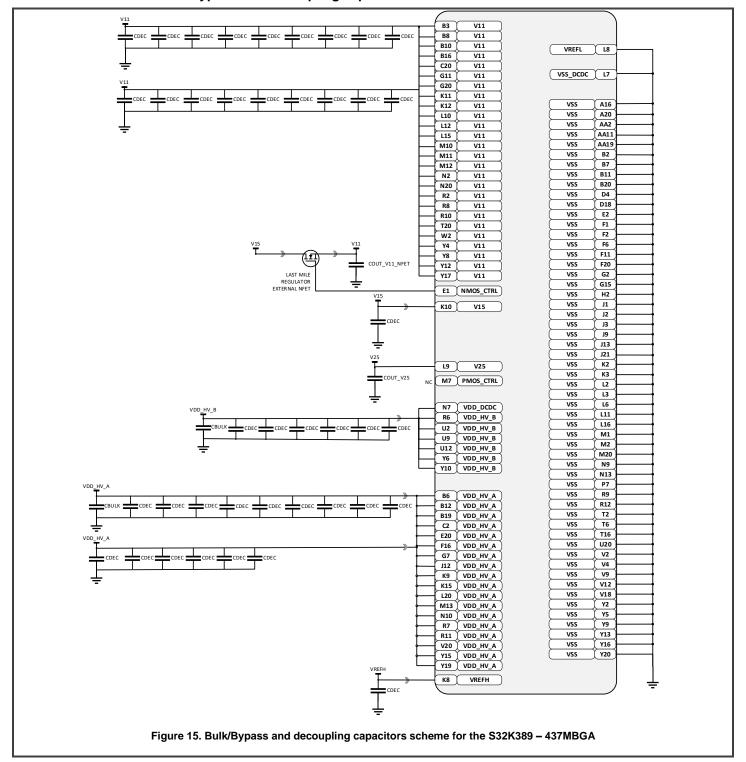

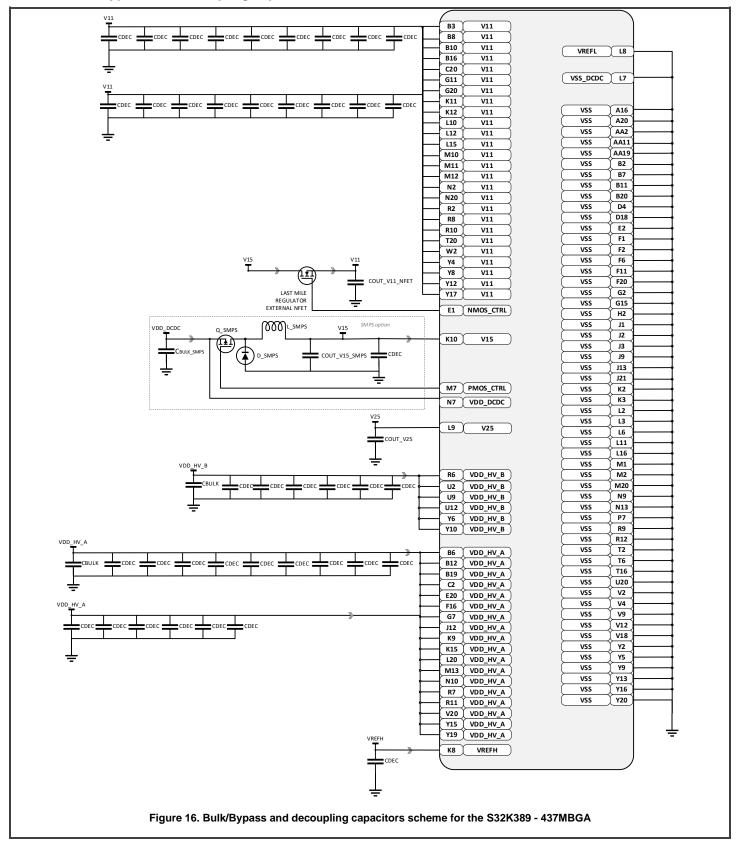

#### 2.1.2.1 Bulk/Bypass and decoupling capacitors scheme for the S32K389 – 437MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 19 / 93

#### 2.1.2.2 Bulk/Bypass and decoupling capacitors scheme for the S32K389 - 437MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 20 / 93

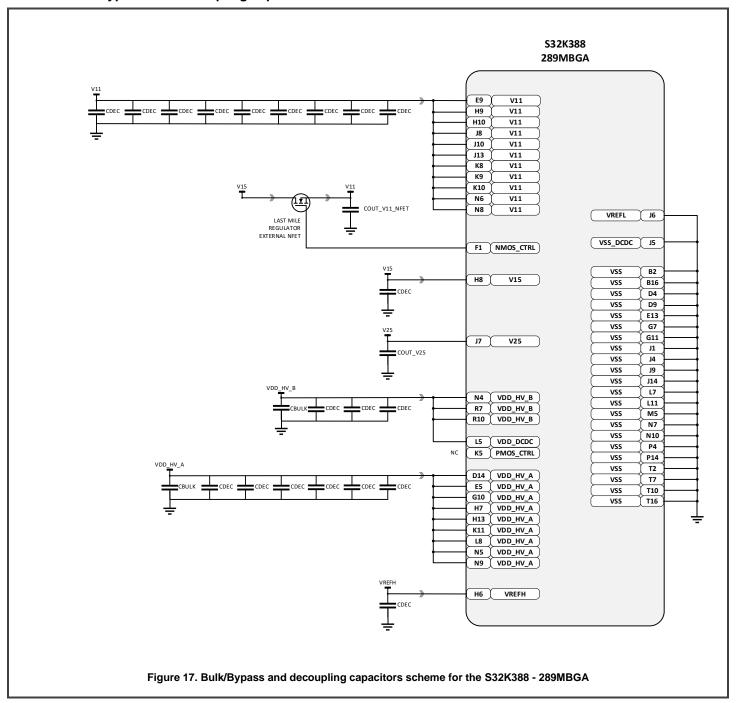

#### 2.1.2.3 Bulk/Bypass and decoupling capacitors scheme for the S32K388 - 289MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 21 / 93

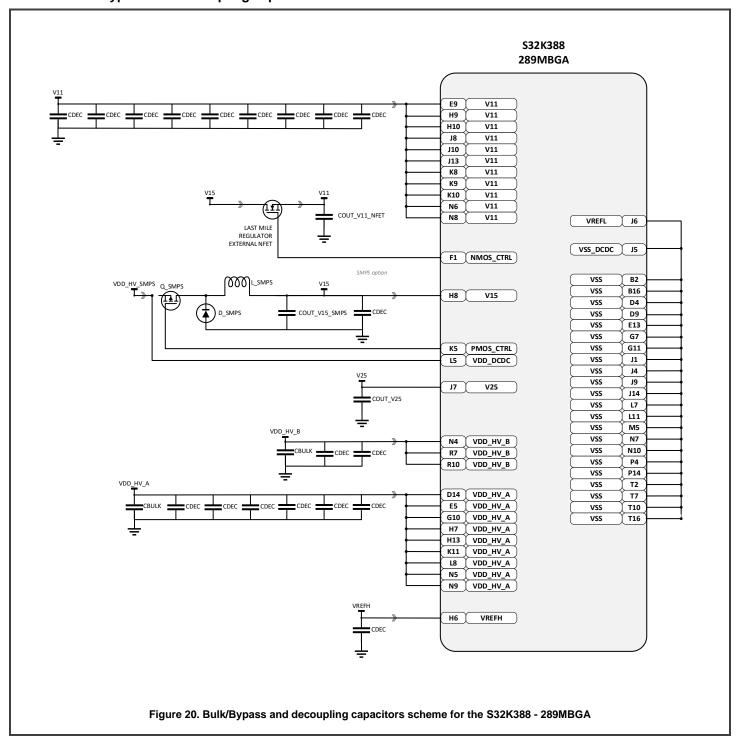

#### 2.1.2.4 Bulk/Bypass and decoupling capacitors scheme for the S32K388 - 289MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 22 / 93

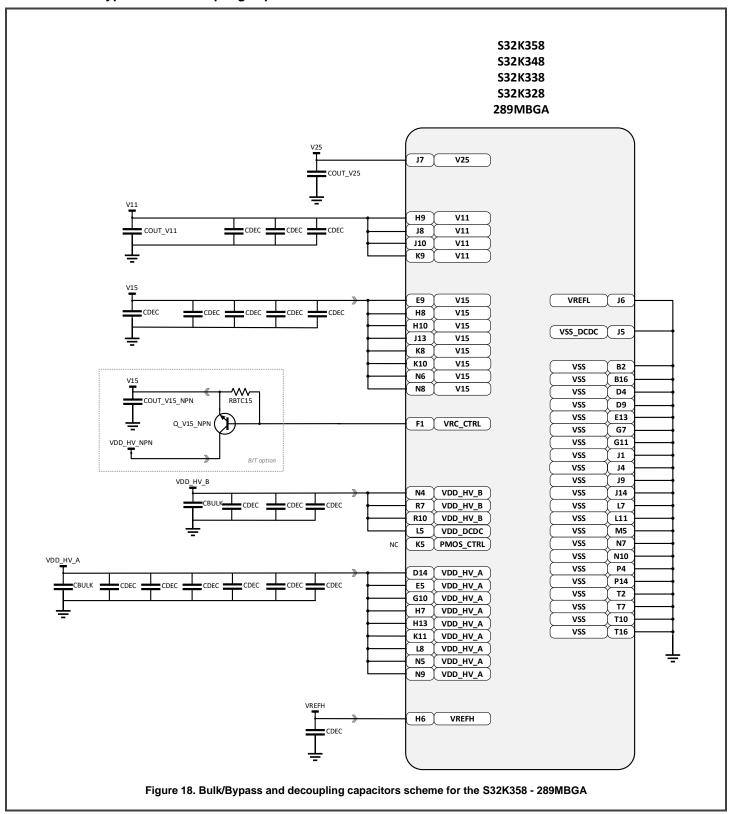

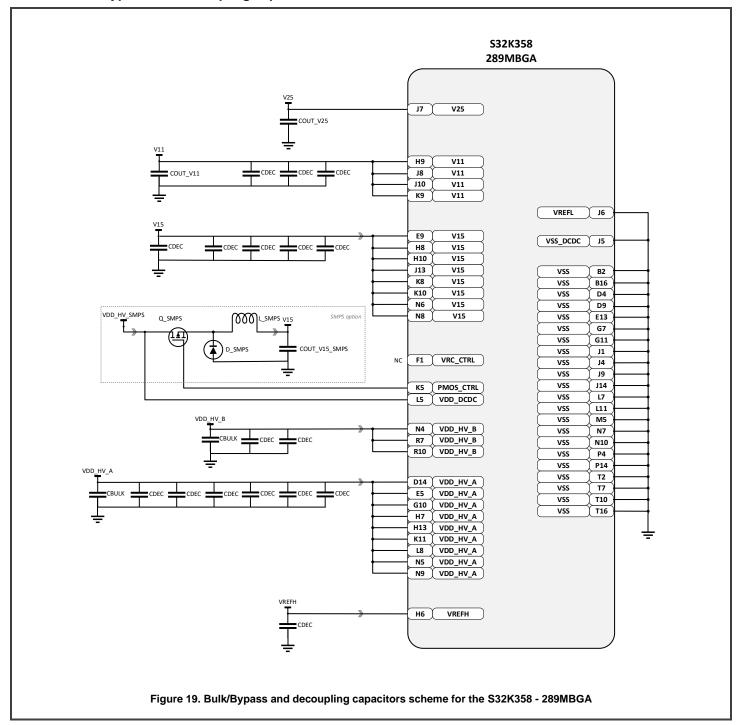

#### 2.1.2.5 Bulk/Bypass and decoupling capacitors scheme for the S32K358 - 289MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 23 / 93

#### 2.1.2.6 Bulk/Bypass and decoupling capacitors scheme for the S32K358 -289MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 24 / 93

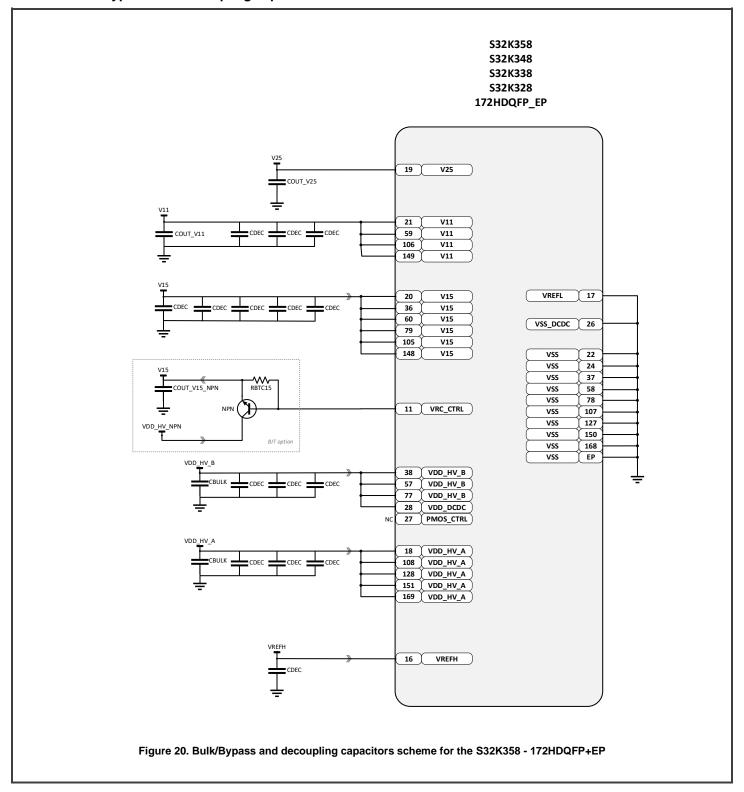

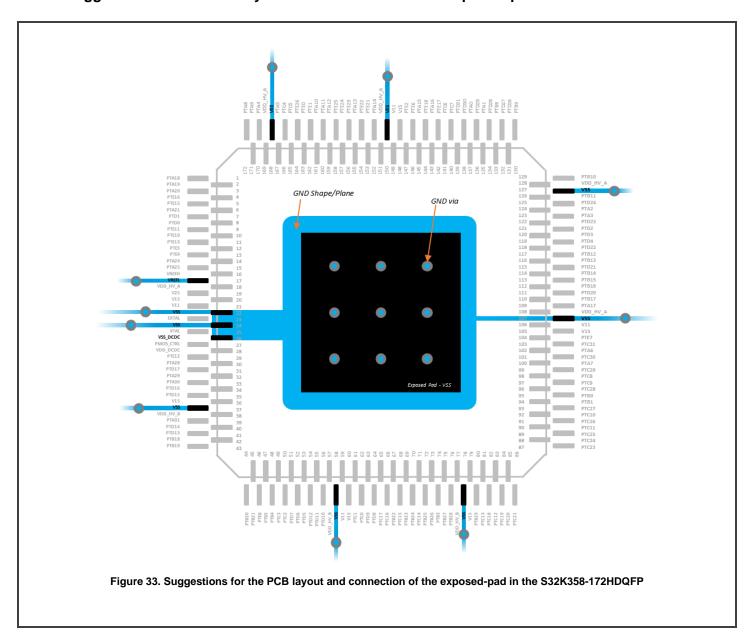

#### 2.1.2.7 Bulk/Bypass and decoupling capacitors scheme for the S32K358 - 172HDQFP+EP

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 25 / 93

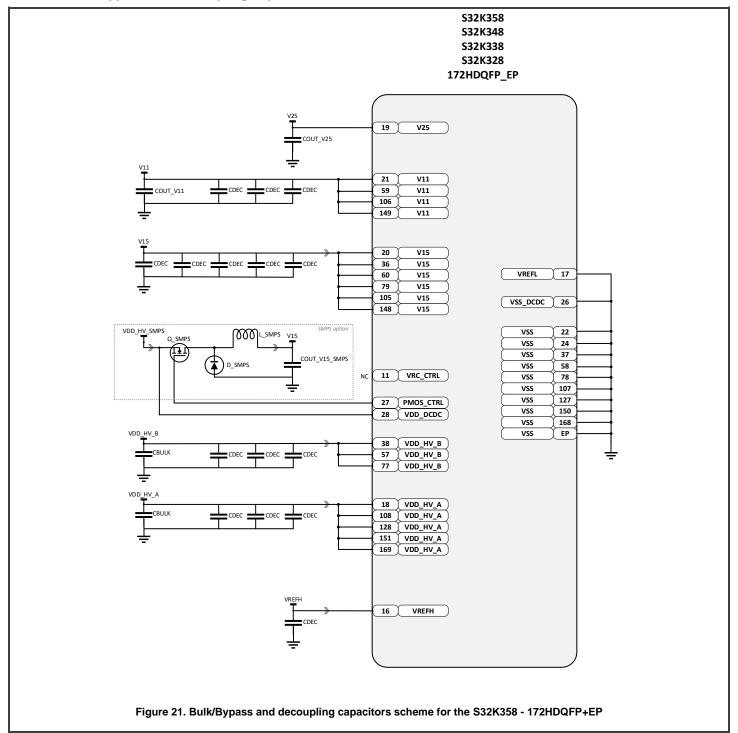

#### 2.1.2.8 Bulk/Bypass and decoupling capacitors scheme for the S32K358 - 172HDQFP+EP

Application Note 26 / 93

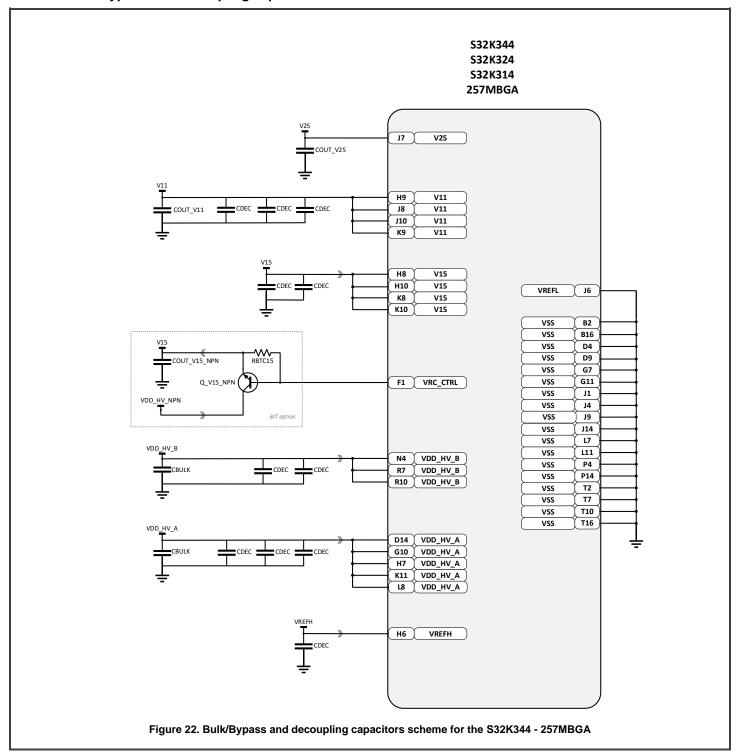

#### 2.1.2.9 Bulk/Bypass and decoupling capacitors scheme for the S32K344 - 257MBGA

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 27 / 93

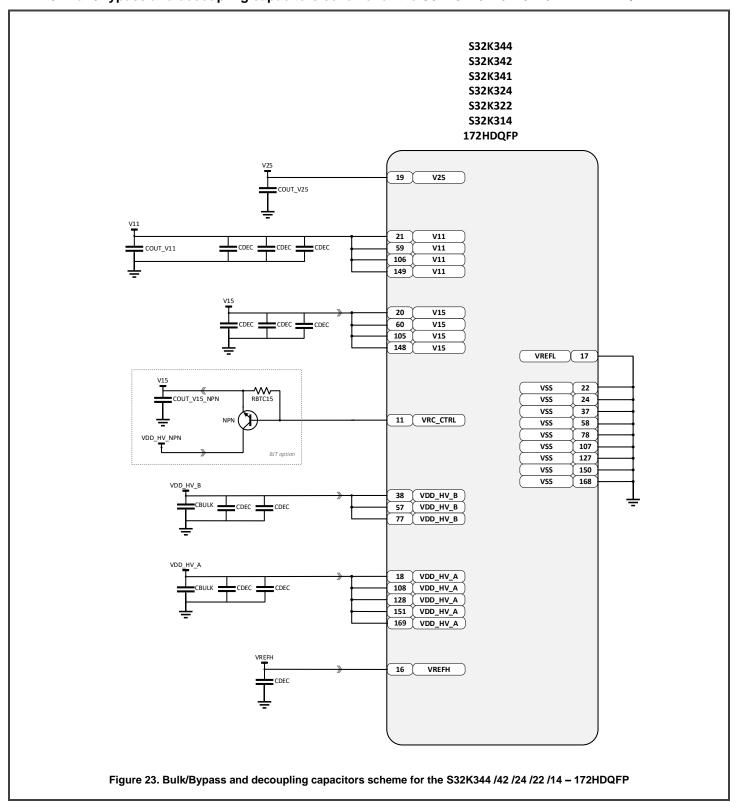

#### 2.1.2.10 Bulk/Bypass and decoupling capacitors scheme for the S32K344 /42 /24 /22 /14 - 172HDQFP

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 28 / 93

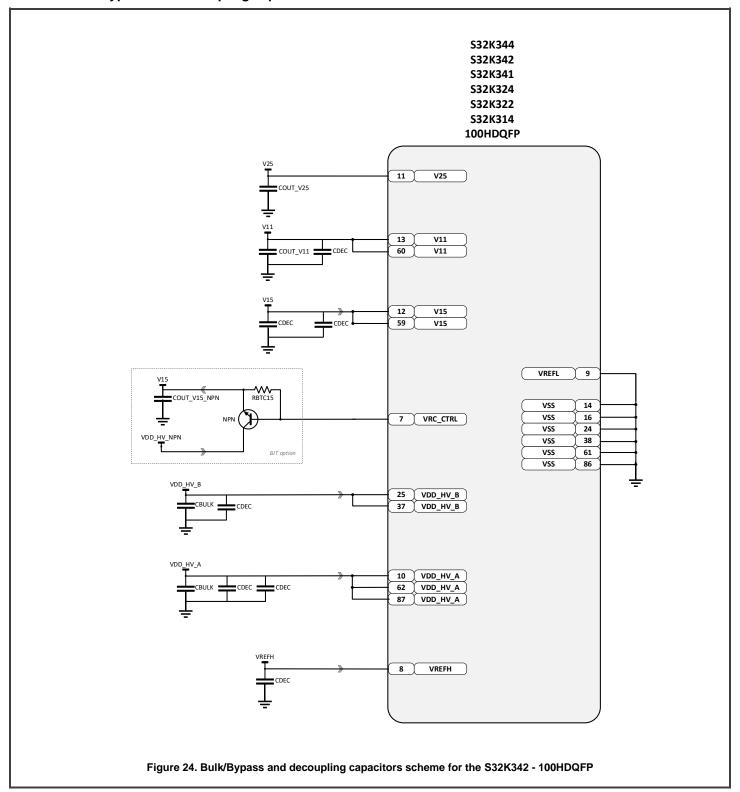

#### 2.1.2.11 Bulk/Bypass and decoupling capacitors scheme for the S32K342 - 100HDQFP

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 29 / 93

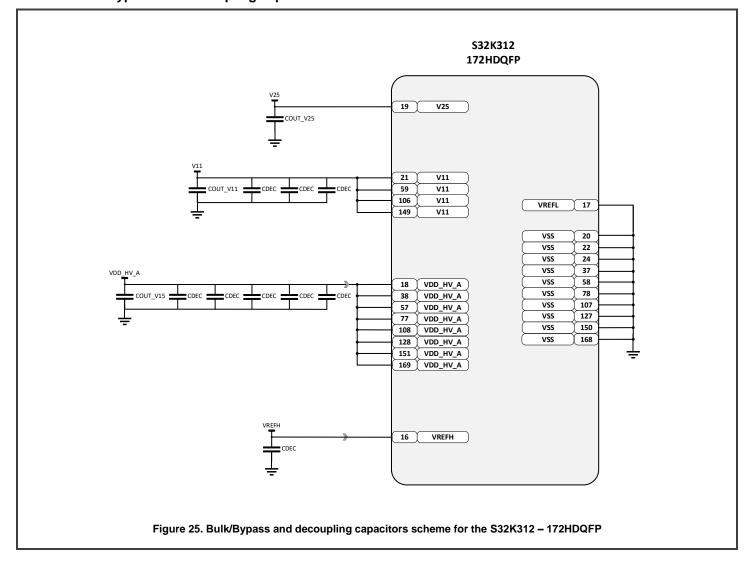

#### 2.1.2.12 Bulk/Bypass and decoupling capacitors scheme for the S32K312 - 172HDQFP

Application Note 30 / 93

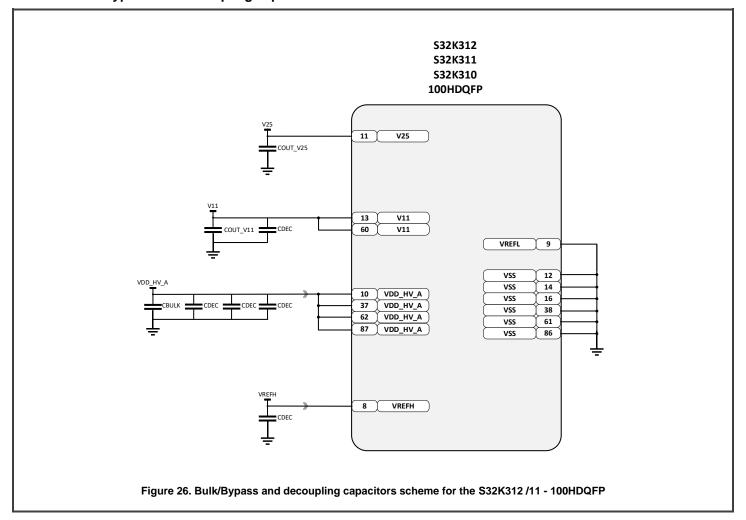

#### 2.1.2.13 Bulk/Bypass and decoupling capacitors scheme for the S32K312 /11 - 100HDQFP

Application Note 31 / 93

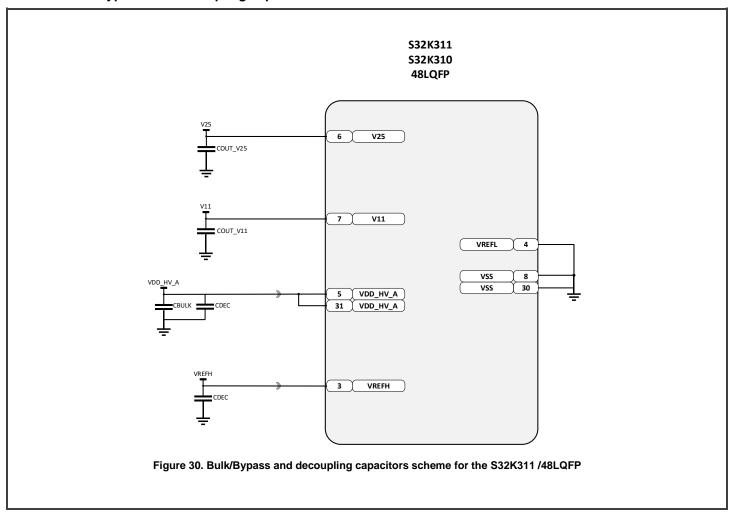

#### 2.1.2.14 Bulk/Bypass and decoupling capacitors scheme for the S32K311 /48LQFP

Table 2. Components description and values

| Symbol                    | Characteristic          | Value         | Description                            |

|---------------------------|-------------------------|---------------|----------------------------------------|

| C <sub>BULK</sub>         | X7R Ceramic or Tantalum | 4.7uF – 10uF  | Local Bulk/Bypass Capacitor for domain |

| C <sub>DEC</sub>          | X7R Ceramic             | 100nF - 220nF | Decoupling Capacitor                   |

| $C_{OUT\_V25}$            | X7R Ceramic             | 220nF         | Decoupling Capacitor for V25           |

| $C_{OUT\_V11}$            | X7R Ceramic or Tantalum | 2.2uF         | Local Bulk/Bypass Capacitor for domain |

| C <sub>OUT_V15_SMPS</sub> | X7S Ceramic             | 20uF - 22uF   | Local Bulk/Bypass Capacitor for domain |

| C <sub>OUT_V11_NFET</sub> | X7R Ceramic             | 22uF          | Local Bulk/Bypass Capacitor for domain |

| R <sub>BCT15</sub>        | Metal Film Resistor     | 2.2kΩ         |                                        |

| Last mile regulator NMOS  | N-Channel Mosfet        |               | External regulator NMOS                |

| Q <sub>NPN15</sub>        | NPN Transistor          |               | NPN Ballast Transistor                 |

|                           | P-Channel Mosfet        |               |                                        |

- 1. All VDD\_HV\_A pins must be shorted and connected externally together to a common and same reference on PCB.

- All VDD\_HV\_B pins must be shorted and connected externally together to a common and same reference on PCB.

- 3. All V11 pins must be shorted and connected externally together to a common and same reference on PCB. This internal reference voltage must not be used or connected to other interfaces in the application.

- 4. All V15 pins must be shorted and connected externally together to a common and same reference on PCB. This internal reference voltage must not be used or connected to other interfaces in the application.

- 5. The V25 is an MCU internal reference voltage that must not be used or connected to other interfaces in the application.

- 6. If the VDD\_HV\_A and VDD\_HV\_B pins are connected to a single voltage reference, just one bulk capacitor is required

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 32 / 93

# 2.2 VDD\_HV\_A - Main I/O and Analog Supply Voltage

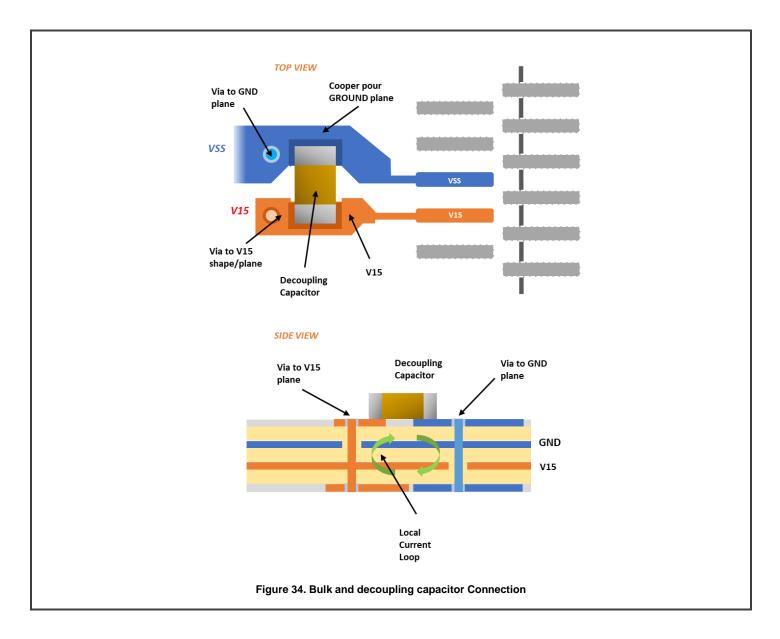

VDD\_HV\_A is the main I/O and analog supply voltage in the S32K3xx MCU. The VDD\_HV\_A domain must be connected to an external power supply of +3.3 V or +5.0V. An off-chip local Bulk/bypass and decoupling capacitors between the VDD\_HV\_A pins and the VSS reference are required. From the Figure 17 to *Figure* are shown the recommended power supply decoupling schemes on the VDD\_HV\_A domain for designs using the S32K3xx MCUs.

Table 3. VDD\_HV\_A - Main I/O and Analog Supply pins

|                    |                                |                          |                               | :                                  | S32K3 N                                                | ICU Pac                    | kage - Pi                         | in Numb                         | er                        |                           |                           |                                                                  |

|--------------------|--------------------------------|--------------------------|-------------------------------|------------------------------------|--------------------------------------------------------|----------------------------|-----------------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|------------------------------------------------------------------|

| MCU<br>Pin<br>Name | Normal<br>Operating<br>Voltage | <b>S32K311</b><br>48LQFP | <b>S32K342/22</b><br>100HDQFP | <b>S32K314 /12 /11</b><br>100HDQFP | <b>S32K344 /42 /24 /22 /14</b><br>172HDQFP - V1.0/V1.1 | <b>S32K312</b><br>172HDQFP | <b>S32K344 /24 /14</b><br>257MBGA | <b>S32K358</b><br>172HDQFP + EP | <b>S32K358</b><br>289MBGA | <b>S32K388</b><br>289MBGA | <b>S32K389</b><br>437MBGA | Comments                                                         |

| VDD_H              | +3.3V                          | 5                        | 10                            | 10                                 | 18                                                     | 18                         | D14                               | 18                              | D14                       | D14                       | B6                        | All VDD_HV_A pins must be                                        |

| V_A                | or<br>+5.0V                    | 31                       | 62                            | 62                                 | 108                                                    | 108                        | G10                               | 108                             | G10                       | G10                       | B12                       | shorted and connected externally together to a common reference  |

|                    | +5.0                           | -                        | 87                            | 87                                 | 128                                                    | 128                        | H7                                | 128                             | H7                        | H7                        | B19                       | on the PCB. A decoupling                                         |

|                    |                                | -                        | -                             | 37                                 | 151                                                    | 151                        | K11                               | 151                             | K11                       | K11                       | C2                        | capacitor can be used per each                                   |

|                    |                                | -                        | -                             | -                                  | 169                                                    | 169                        | L8                                | 169                             | L8                        | L8                        | E20                       | supply pin and a local Bulk/bypass                               |

|                    |                                | -                        | -                             | -                                  | -                                                      | 38                         | -                                 | -                               | H13                       | H13                       | F16                       | capacitor just for the VDD_HV_A domain, in order to increase the |

|                    |                                | -                        | -                             | -                                  | -                                                      | 57                         | -                                 | -                               | E5                        | E5                        | G7                        | robustness and decoupling effect                                 |

|                    |                                | -                        | -                             | -                                  | -                                                      | 77                         | -                                 | -                               | N5                        | N5                        | J12                       | on this voltage reference of the                                 |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | N9                        | N9                        | K9                        | MCU.                                                             |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | K15                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | L20                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | M13                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | N10                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | R7                        |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | R11                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | V20                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | Y15                       |                                                                  |

|                    |                                | -                        | -                             | -                                  | -                                                      | -                          | -                                 | -                               | -                         | -                         | Y19                       |                                                                  |

Application Note 33 / 93

#### 2.3 VREFH - ADC High Reference Voltage

VREFH is the ADC High Reference Voltage. An off-chip decoupling capacitor between the VREFH pin and the VSS/VREFL reference are required.

The VREFH is the ADC High Reference Voltage in the S32K3xx MCU. The VREFH pin must be connected to an external power supply or a reference voltage  $\leq$  VDD\_HV\_A. An off-chip local decoupling capacitor between the VREFH pin and the VSS/VREFL reference is required. From the *Figure 17* to Figure are shown the recommended power supply decoupling scheme on the VREFH pin for designs using the S32K3xx MCUs.

Table 4. VREFH - ADC High Reference Voltage

|                    |                                |                          |                               | S                                  | 32K3 M                                                 | CU Pack                    | age - Pir                         | Numbe                           | r                         |                           |                           |                                                        |

|--------------------|--------------------------------|--------------------------|-------------------------------|------------------------------------|--------------------------------------------------------|----------------------------|-----------------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|--------------------------------------------------------|

| MCU<br>Pin<br>Name | Normal<br>Operating<br>Voltage | <b>S32K311</b><br>48LQFP | <b>S32K342/22</b><br>100HDQFP | <b>S32K314 /12 /11</b><br>100HDQFP | <b>S32K344 /42 /24 /22 /14</b><br>172HDQFP - V1.0/V1.1 | <b>S32K312</b><br>172HDQFP | <b>S32K344 /24 /14</b><br>257MBGA | <b>S32K358</b><br>172HDQFP + EP | <b>S32K358</b><br>289MBGA | <b>S32K388</b><br>289MBGA | <b>S32K389</b><br>437MBGA | Comments                                               |

| VREFH              | ≤VDD_HV_<br>A                  | 3                        | 8                             | 8                                  | 16                                                     | 16                         | H6                                | 16                              | H6                        | H6                        | K8                        | A decoupling capacitor must be used on the supply pin. |

| VREFL              | GND                            | 4                        | 9                             | 9                                  | 17                                                     | 17                         | J6                                | 17                              | J6                        | J6                        | L8                        | Refers the section VSS,                                |

|                    |                                |                          |                               |                                    |                                                        |                            |                                   |                                 |                           |                           |                           | VSS_DCDC and VREFL – Ground and ADC Reference Low.     |

Application Note 34 / 93

#### 2.4 VDD\_HV\_B - Secondary I/O Supply Voltage

The VDD\_HV\_B is the secondary I/O Supply voltage in some versions of the S32K3xx MCU family. The VDD\_HV\_B domain must be connected to an external power supply of +3.3 V or +5.0V. An off-chip local Bulk/bypass and decoupling capacitors between the VDD\_HV\_B pins and the VSS reference are required. From the Figure 17 to *Figure* are shown the recommended power supply decoupling schemes on the VDD\_HV\_B domain for designs using the S32K3xx MCUs.

Table 5. VDD\_HV\_B - Secondary I/O Supply Voltage

|                 |                                |                          |                                | S                              | 32K3 MC                                                      | U Pack                     | age - P                           | in Num                          | ber                       |                           |                           |                                                                                     |  |  |  |

|-----------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|--------------------------------------------------------------|----------------------------|-----------------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|-------------------------------------------------------------------------------------|--|--|--|

| MCU<br>Pin Name | Normal<br>Operating<br>Voltage | <b>S32K311</b><br>48LQFP | <b>S32K342 /22</b><br>100HDQFP | <b>S32K312 /11</b><br>100HDQFP | <b>S32K344 /42 /24 /22 /14</b><br>172HDQFP<br>V1 0 and V1 11 | <b>S32K312</b><br>172HDQFP | <b>S32K344 /24 /14</b><br>257MBGA | <b>S32K358</b><br>172HDQFP + EP | <b>S32K358</b><br>289MBGA | <b>S32K388</b><br>289MBGA | <b>S32K389</b><br>437MBGA | Comments                                                                            |  |  |  |

| VDD_HV_B        | +3.3V                          | -                        | 25                             | -                              | 38                                                           | -                          | N4                                | 38                              | N4                        | N4                        | R6                        | All VDD_HV_B pins must be shorted                                                   |  |  |  |

|                 | or<br>+5.0V                    | -                        | 37                             | -                              | 57                                                           | -                          | R7                                | 57                              | R7                        | R7                        | U2                        | and connected externally together to a common reference on the PCB. A               |  |  |  |

|                 | +5.07                          | -                        | -                              | -                              | 77                                                           | -                          | R10                               | 77                              | R10                       | R10                       | U9                        | decoupling capacitor can be used per                                                |  |  |  |

|                 |                                | -                        | -                              | -                              | -                                                            | •                          | -                                 | -                               | •                         | -                         | U12                       | each supply pin and a local                                                         |  |  |  |

|                 |                                | -                        | -                              | -                              | -                                                            | -                          | -                                 | -                               | -                         | -                         | Y6                        | Bulk/bypass capacitor just for the VDD_HV_B domain, in order to                     |  |  |  |

|                 |                                | -                        | -                              | -                              | -                                                            | -                          | -                                 | -                               | -                         | -                         | Y10                       | increase the robustness and decoupling effect on this voltage reference of the MCU. |  |  |  |

#### 2.5 V11 - Core logic voltage supply (+1.1 V)

V11 is the internally generated core logic voltage supply, except for the S32K388 and S32K389 version. And an off-chip Bulk/bypass, decoupling and filter capacitors between the V11 pins and the VSS reference is highly recommended. From the Figure 17 to *Figure* are shown the recommended power supply decoupling schemes on the V11 pin for designs using the S32K3xx MCUs. This reference voltage must not be used or connected to other interfaces in the application.

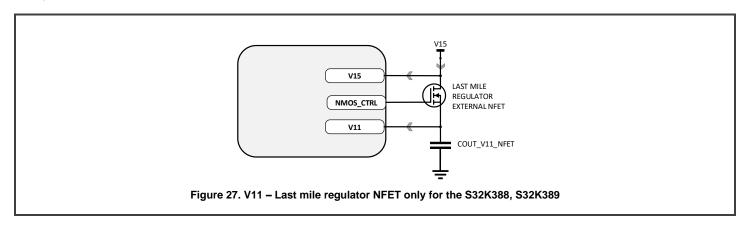

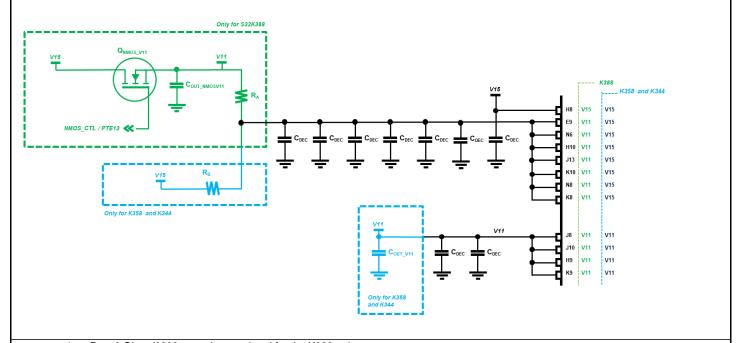

#### 2.5.1 Last Mile Regulator External NFET V11 supply for S32K388, S32K389 version

For the S32K388, S32K389, the V11 must be externally generated for core supply by an NMOS at the output of the V15 supply, additionally must connect a stability and decoupling capacitors between the V11 pin and the VSS reference are required. This reference voltage must not be used or connected to other interfaces in the application.

Hardware Design Guidelines for S32K3 Microcontrollers, Rev. E2, March. 2025

Application Note 35 / 93

Table 6. V11 - Core logic voltage supply (+1.1 V)

| MCU<br>Pin<br>Name                                       | Normal<br>Operating<br>Voltage            | S32K3 MCU Package - Pin Number |                                |                                    |                                                              |                            |                                   |                                 |                           |                           |                           |                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------|-------------------------------------------|--------------------------------|--------------------------------|------------------------------------|--------------------------------------------------------------|----------------------------|-----------------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          |                                           | <b>S32K311</b><br>48LQFP       | <b>S32K342 /22</b><br>100HDQFP | <b>S32K314 /12 /11</b><br>100HDQFP | <b>S32K344 /42 /24 /22 /14</b><br>172HDQFP<br>V1.0 and V1.1] | <b>S32K312</b><br>172HDQFP | <b>S32K344 /24 /14</b><br>257MBGA | <b>S32K358</b><br>172HDQFP + EP | <b>S32K358</b><br>289MBGA | <b>S32K388</b><br>289MBGA | <b>S32K389</b><br>437MBGA | Comments                                                                                                                                                                                                                                                                                                               |

| V11 <sup>[1]</sup>                                       | +1.1V Internal voltage reference          | 7                              | 13                             | 13                                 | 21                                                           | 21                         | H9                                | 21                              | H9                        | E9                        | B3                        | All V11 pins must be shorted and connected externally together to a common reference on the PCB. A decoupling capacitor can be used per each supply pin and a local Bulk/bypass capacitor just for the V11 domain, in order to increase the robustness and decoupling effect on this voltage reference of the MCU. [1] |

|                                                          |                                           | -                              | 60                             | 60                                 | 59                                                           | 59                         | J8                                | 59                              | J8                        | H9                        | B8                        |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | 106                                                          | 106                        | J10                               | 106                             | J10                       | H10                       | B10                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | 149                                                          | 149                        | K9                                | 149                             | K9                        | J8                        | B16                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | J10                       | C20                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | J13                       | G11                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | K8                        | G20                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | K9                        | K11                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | K10                       | K12                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | N6                        | L10                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | N8                        | L12                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | -                         | L15                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | -                         | M10                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | -                         | M11<br>M12                |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | -                               | -                         | -                         | N2                        |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | _                              | _                              | -                                  | -                                                            |                            | -                                 |                                 | -                         | -                         | N20                       |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | _                              | -                                  | -                                                            |                            | -                                 |                                 | -                         | -                         | R2                        |                                                                                                                                                                                                                                                                                                                        |

|                                                          |                                           | -                              | -                              | -                                  | -                                                            | -                          | -                                 | <u> </u>                        | -                         | -                         | R8                        |                                                                                                                                                                                                                                                                                                                        |

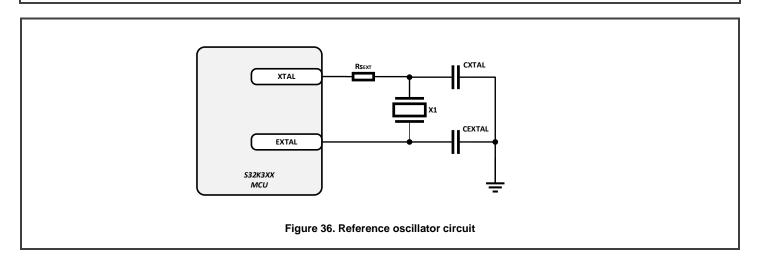

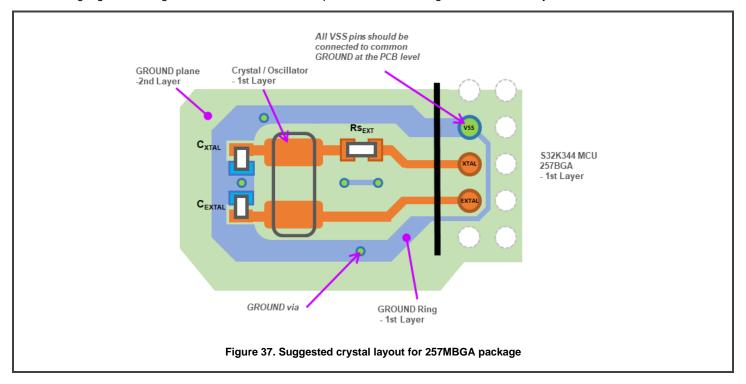

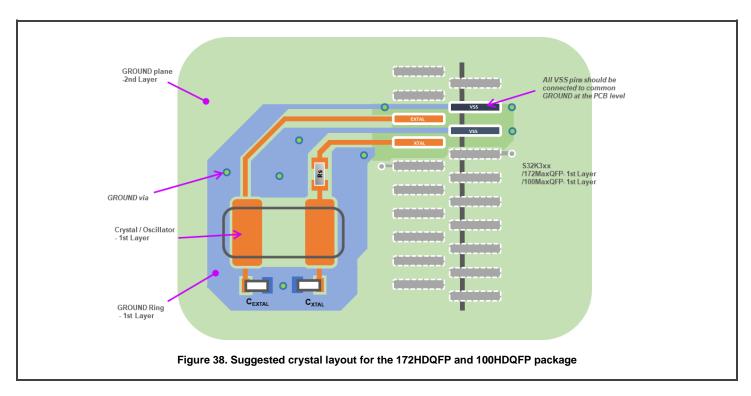

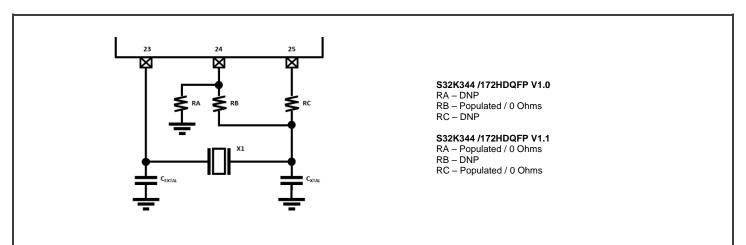

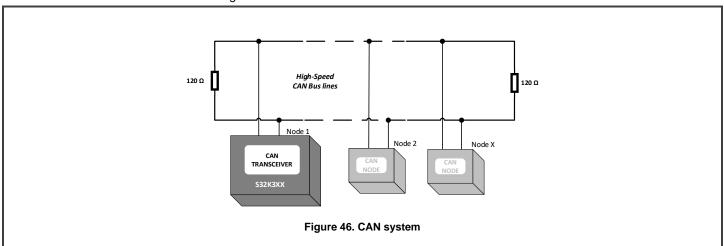

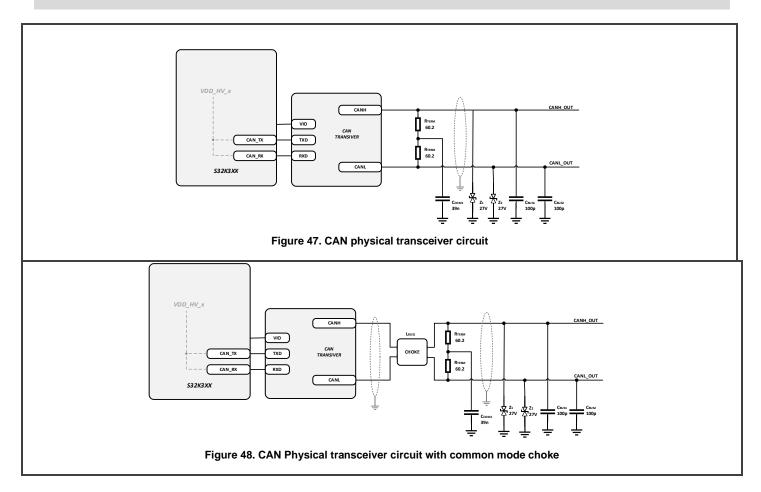

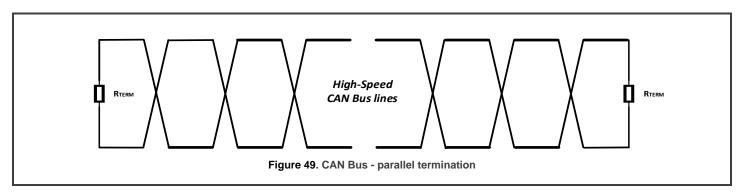

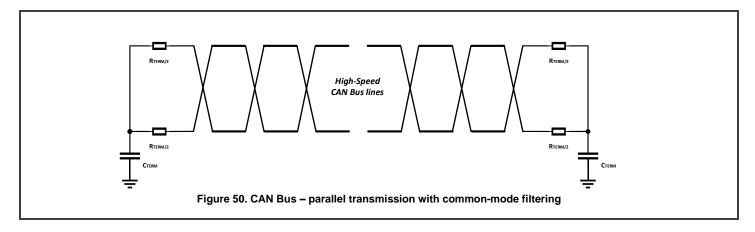

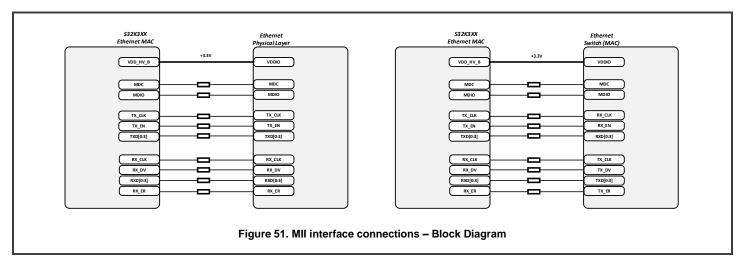

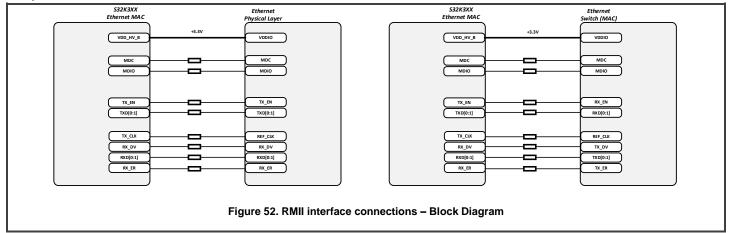

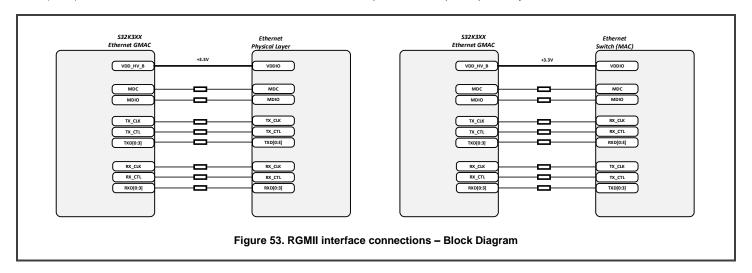

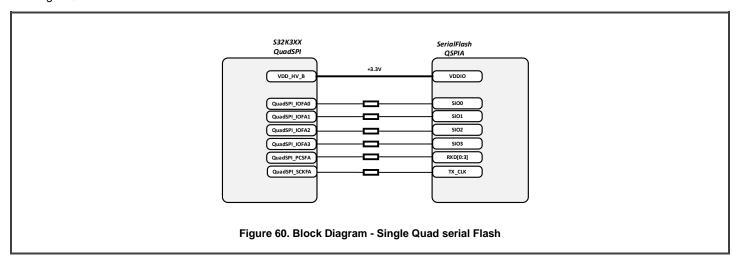

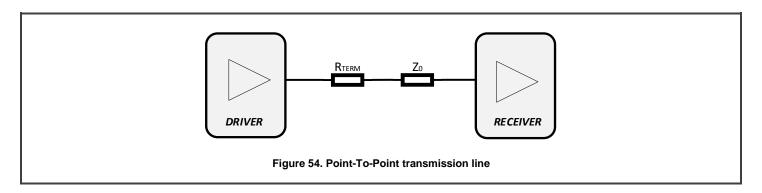

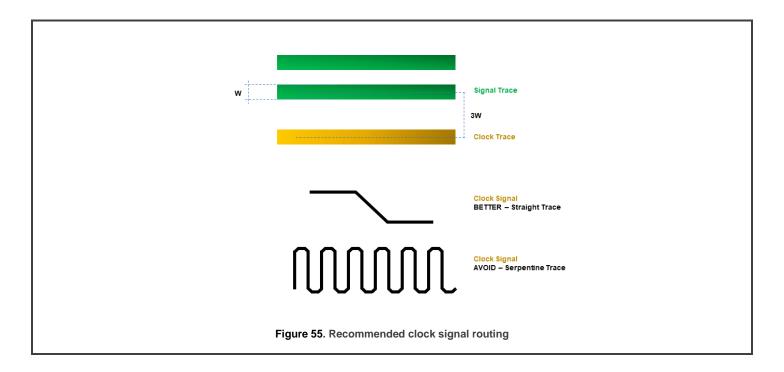

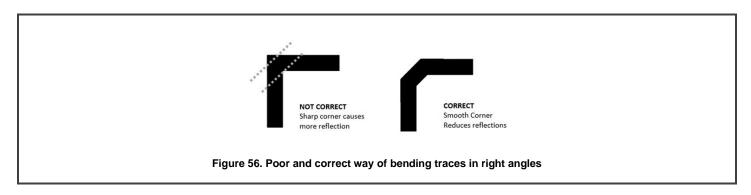

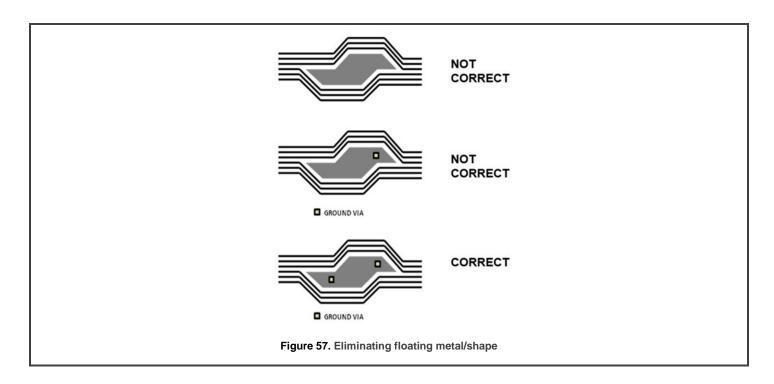

|                                                          |                                           | _                              | _                              | _                                  | _                                                            |                            | _                                 |                                 | _                         | _                         | R10                       |                                                                                                                                                                                                                                                                                                                        |